ADC学习总结

ADC的架构分类:

1、Delta-Sigma

采样率一般是在1M以内,位数一般可以做的很高,比如24位,Delta-Sigma ADC采用了过采样技术,不需要在模拟输入端加抗混叠滤波,由后端数字滤波器进行处理,通过信噪比=6.02*N + 1.76 + 10log(fs / 2BW)可知,fs增加4倍,就是多加一个6.02,有效位N就要加一, Delta-Sigma ADC就是通过过采样来提升有效位。由于采样率较低,有效位数较高的特点, Delta-Sigma ADC在静态精密测量的场合应用非常广泛,比如在锂电池充放电检测设备,PLC的模拟量模块中,都有广泛的应用。

Delta-Sigma ADC的电路原理理解参考:

信噪比6.02*N + 1.76 + 10log(fs / 2BW)的来源参考:

2、SAR

采样率最大10M左右,常见最大位数18位,SAR ADC是一个位数、采样率都不高不低的ADC,具有低功耗,尺寸小的特点,也是目前应用最广泛的ADC。

SAR ADC的原理介绍参考:

3、FLASH

闪速ADC是目前转换速度最快的ADC,缺点就是位数一般最大就是10位左右,闪速ADC由大量的比较器构成,N位ADC就要有2^N-1个比较器,8位闪速ADC就要有255个比较器,虽然使用一些方法可以减少一些比较器的数量。

闪速ADC的原理介绍参考:

Flash_ADC的电路原理_flash电路原理-CSDN博客

4、Folding

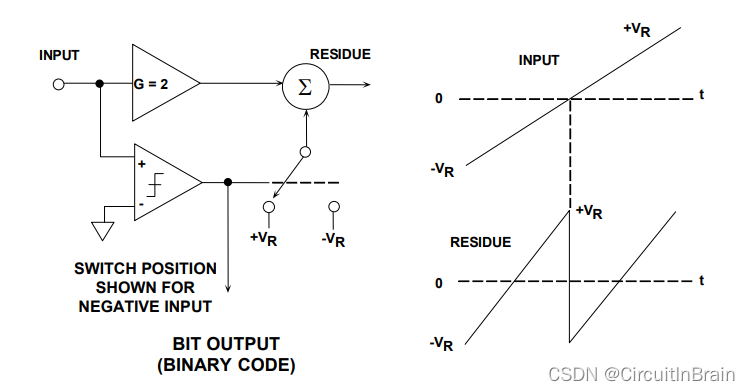

折叠式ADC主要思想就是分区、再组合,先将输入电压分成两路信号,一路直接通过低精度Flash ADC,进行粗量化,得到高位的MSB;另外一路通过折叠放大器分成小的量化区间再进行细量化。下图为单个二进制位转换的基本级,由一个2倍增益放大器,一个比较器,一个1位的DAC构成,比较器输出控制1位ADC,残余的输出由放大器输出和DAC输出叠加,然后传到下一级。

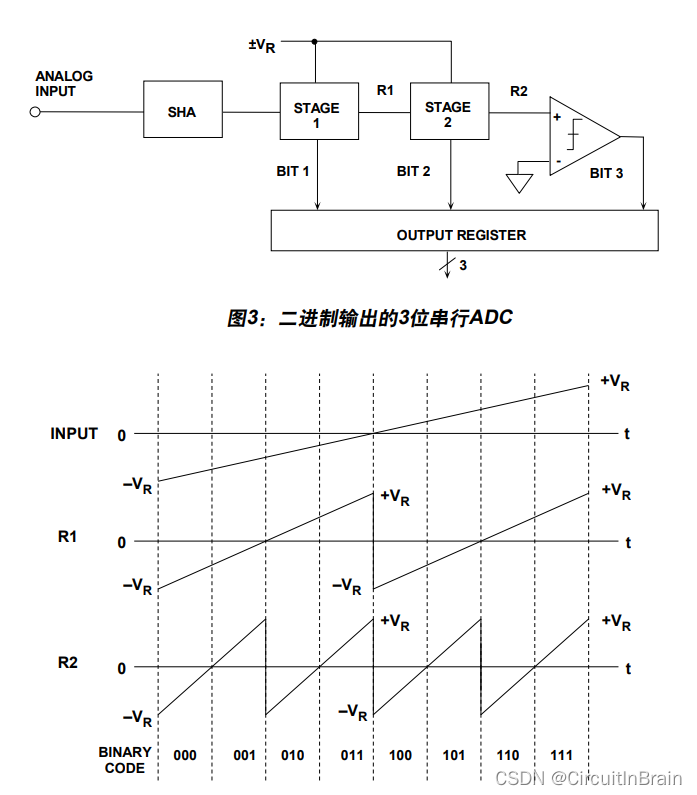

下图为1个3位串型结构的Folding ADC,有两个二进制转换的基本级构成,两个基本级并行进行。

?详细原理参考:

https://www.analog.com/media/cn/training-seminars/tutorials/mt-025_cn.pdf

5、Pipeline?

Pipeline架构的来源于分级结构的ADC,核心的思想就是:量化,提取误差,对误差进行量化,再提取 误差,再量化…,

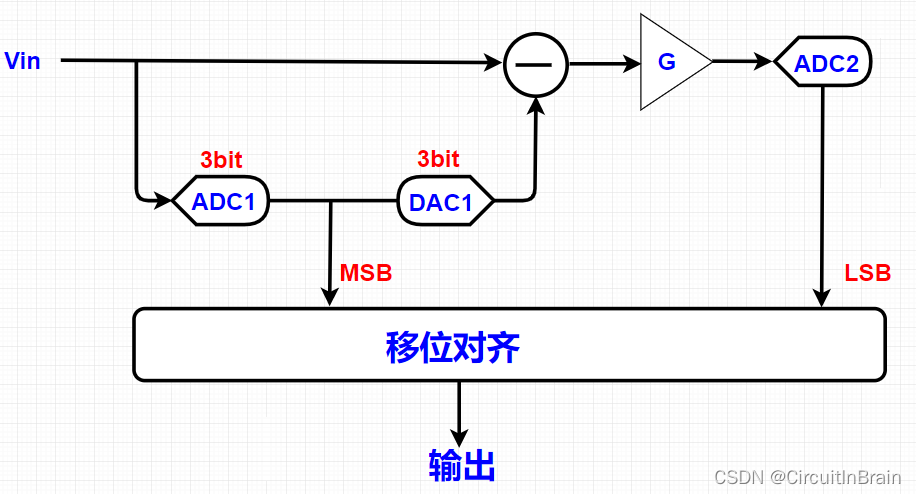

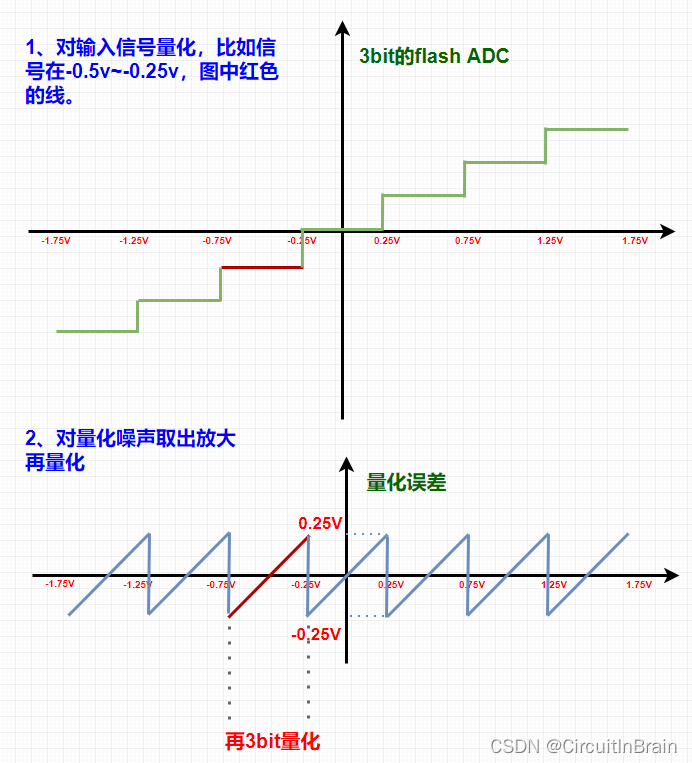

下面以一个6bit的两级ADC为例说明,第一级是输入信号先经过一个3bit的flash ADC对输入信号进行一个粗的量化,输出高3位的码值,再用输入信号与高3位的码值的DAC输出做差,这个差也就是量化噪声,这个量化噪声再进入一个3bit的flash ADC,得到低3位的码值。

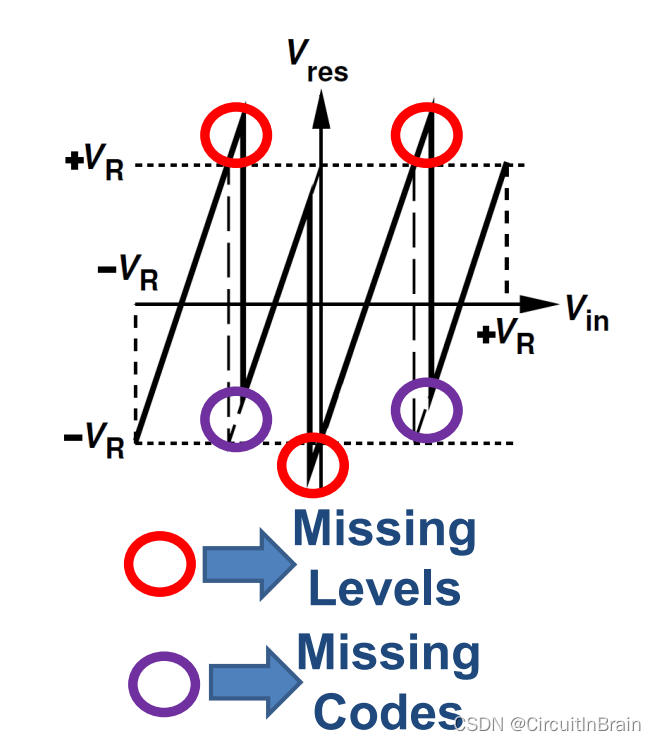

?Pipeline用到的冗余技术

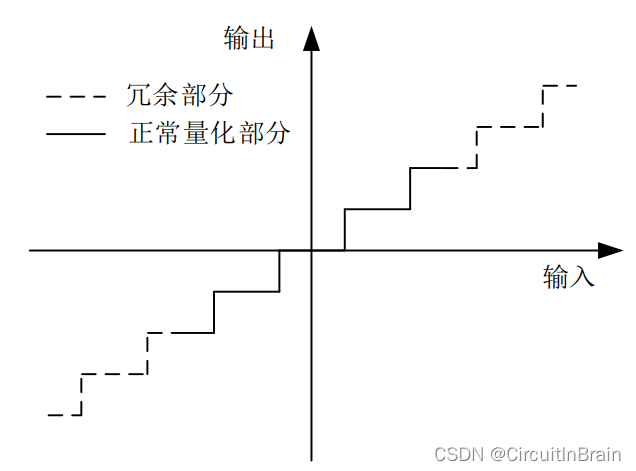

因为要取出量化残差放大后精确的对准下一级的输入范围,这个对准可能会出现问题,所以可以对放大倍数做一点缩小,增加冗余,在没有任何误差情况下,量化余差曲线只会用到下图的实线部分,一旦比较器发生失调,余差曲线会超出正常范围,超出的部分由冗余部分进行量化,以此达 到校准目的。

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 图:残差的对准问题

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 图:增加冗余

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!