Marin说PCB之电源完整性之直流压降仿真CST--02

? ? ?上回书说到了电源直流压降仿真的操作步骤了,本编文章小编我继续给大家分析一下如何去看这些仿真报告数据以及我们应该如何去改善那些直流压降不满足误差值的情况了。

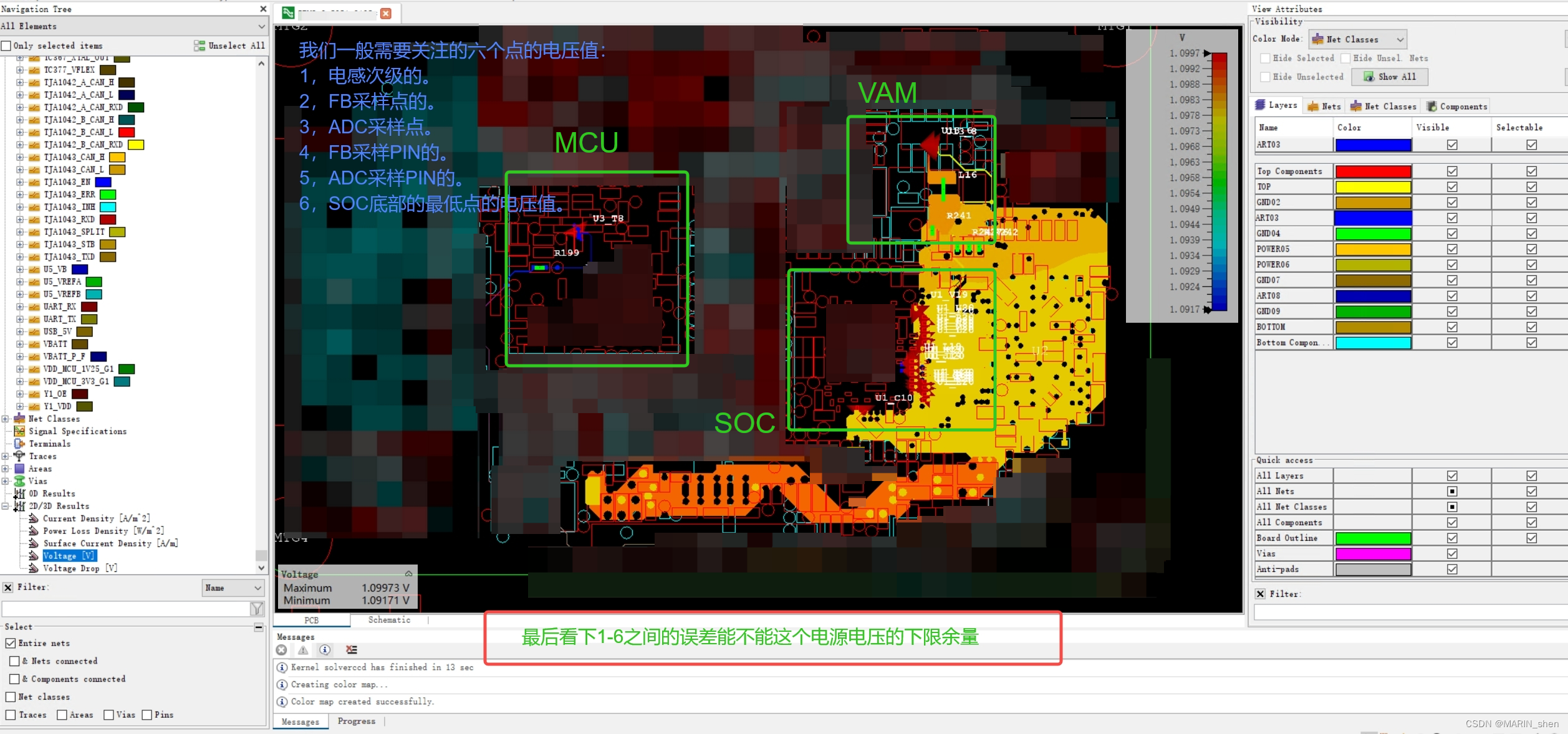

1,首先我们要知道我们仿真结束后需要关注的哪些点的电压值。我们在0D界面是可以看到你之前设置的所有负载端口和分离元器件上的电压值的情况的,如下如所示:

2,其次就是我们需要关注的有六个地方的电压值:

? A,电感次级端口。

??B,FB采样点的。

?C,ADC采样点的。

?D,FB采样PIN的。

?E,ADC采样PIN的。

?F,SOC底部最低点的电压值。

??? ?

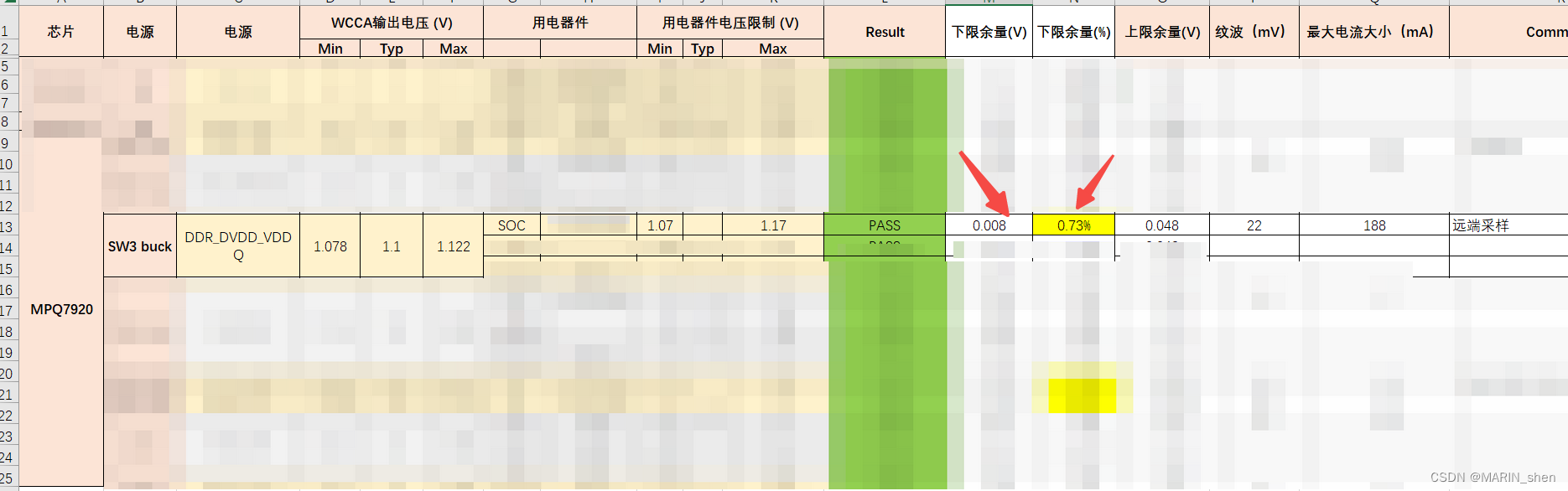

3,我们的设计要求是A~F之间的误差为0.73%,我们把这六个点的电压值测量好后对比一下是满足这个误差要求的,即这个电源网络的直流压降是PASS的。

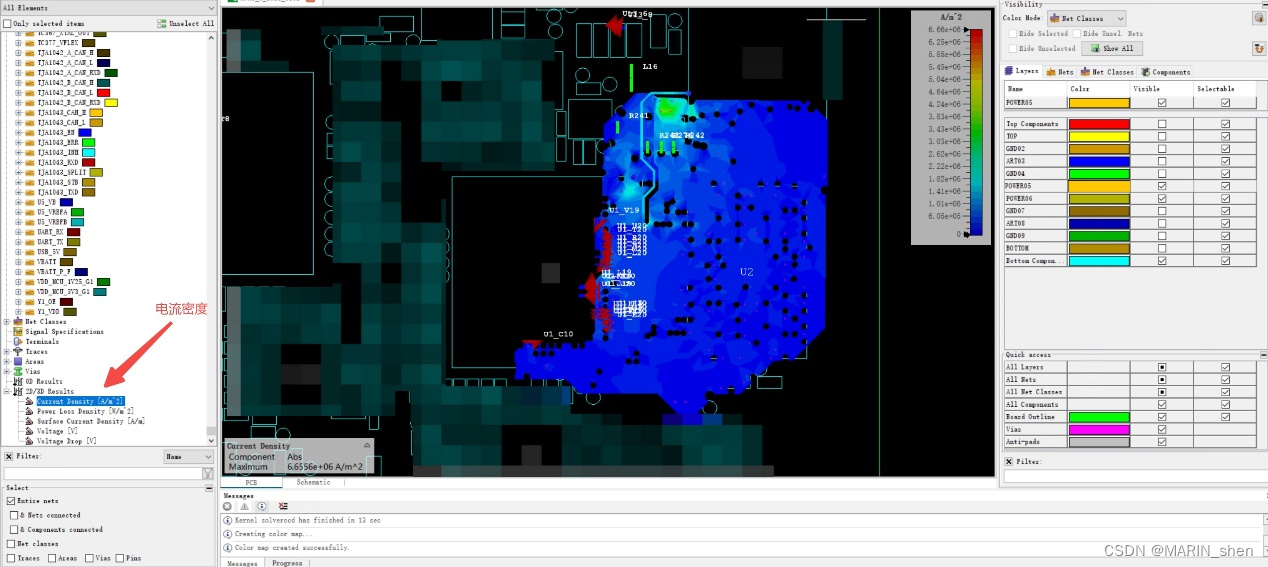

4,仿真的时候还需要关注的一点就是电流密度,通过电流密度的分布我们来判断铺铜路径的瓶颈区,以此来优化我们PCB设计。

其实我们常说的电流密度是指单位面积内通过的电流量。它是描述电流在空间分布情况的物理量。电流密度的计算公式为电流除以通过的横截面积。电流密度的单位通常为安培/平方米(A/m^2)或安培/平方厘米(A/cm^2)。

电流密度的计算公式如下: 电流密度(J)= 电流(I)/ 横截面积(A)

其中,电流(I)是通过某一横截面的电流量,横截面积(A)是电流通过的横截面的面积。下面我们就举个例子来说一下。

如果通过一个导线的电流为2安培,而导线的横截面积为0.5平方米,则该导线的电流密度为4安培/平方米。

当电流通过一个狭窄区域的时候,通常会产生较大的电流 密度,从而导致PCB板局部温度的升高。

1,电源平面上最大的电流密度区域通常称之为电流热点 (Hot Spot),这些电流热点有可能导致严重的热可靠性 问题。

?2,设计人员应尽量使板上的电流密度分布均匀, 并且最大值尽量不要超过常用的经验门限100A/mm2。

那我们应该如何改善我们PCB板子上存在着过高的电流密度分布呢?为了阻止直流压降的发生,我们可以考虑以下两种方案:

1,使用更大的导体截面积:增加导体的截面积可以降低电阻,从而减小电压降。这样可以通过减小电流密度来降低直流压降。这个在我们改PI电源工程师意见的时候遇到的最多的就是加宽你的电源布线通道。这个有一点需要注意的就是你要加宽的电源通道一定的电源流向的最小的通道。

我经常会遇到一些layout同事在改客户那边电源意见的时候说我已经把这个core电源加了很宽了,这个电源网络的直流压降应该没有问题了吧,可是等到PI工程师检查的时候差点气的吐血。

?

2,优化导体材料:选择具有较低电阻率的导体材料可以减小电阻,从而减小电压降。这样也可以通过减小电流密度来降低直流压降。(这个一般实用性感觉不是很大前期EE同事那边其实都已经选好了器件,后面再去改就比较麻烦了,而且遇到那些电感,电阻还是呆滞料的话就更加麻烦了)

5,还有就是我们在做PCB设计的时候往往只是关注那些低电压大电流的网络,经常忽略那些电流大的网络了,例如我们有时候把那些电源芯片输出的LDO的电源网络就直接走线15MIL,而且还走线很长。

?

这种做法你感觉是负载电流才MA级别的应该问题不大的,实际上由于你的PCB上走线过长,而且走线又不是很粗,很容易产生直流压降超标的问题的。

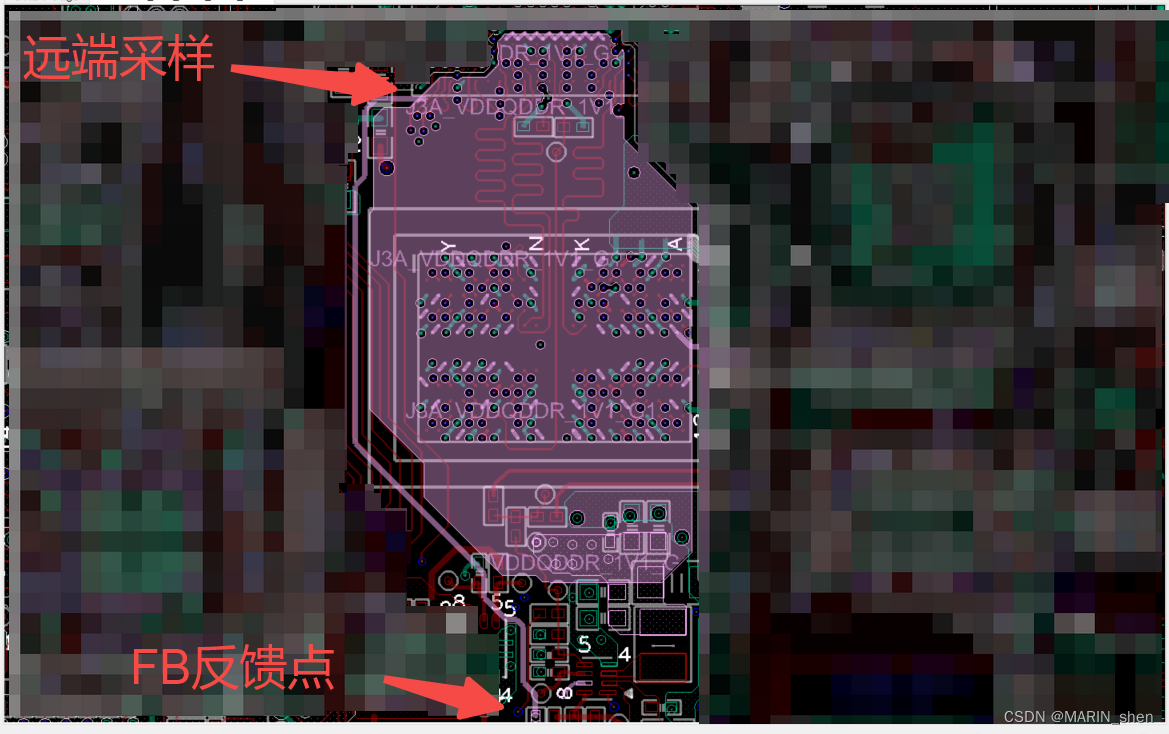

6,有的时候我们遇到PCB板子上的空间很挤了,再去加宽我们的铺铜已经是不太可能了,这个时候我们可以试着通过对电源实施远端补偿也就是我们常说FB远端在SOC端口那边采样的方法来提升我们负载的供电电压。

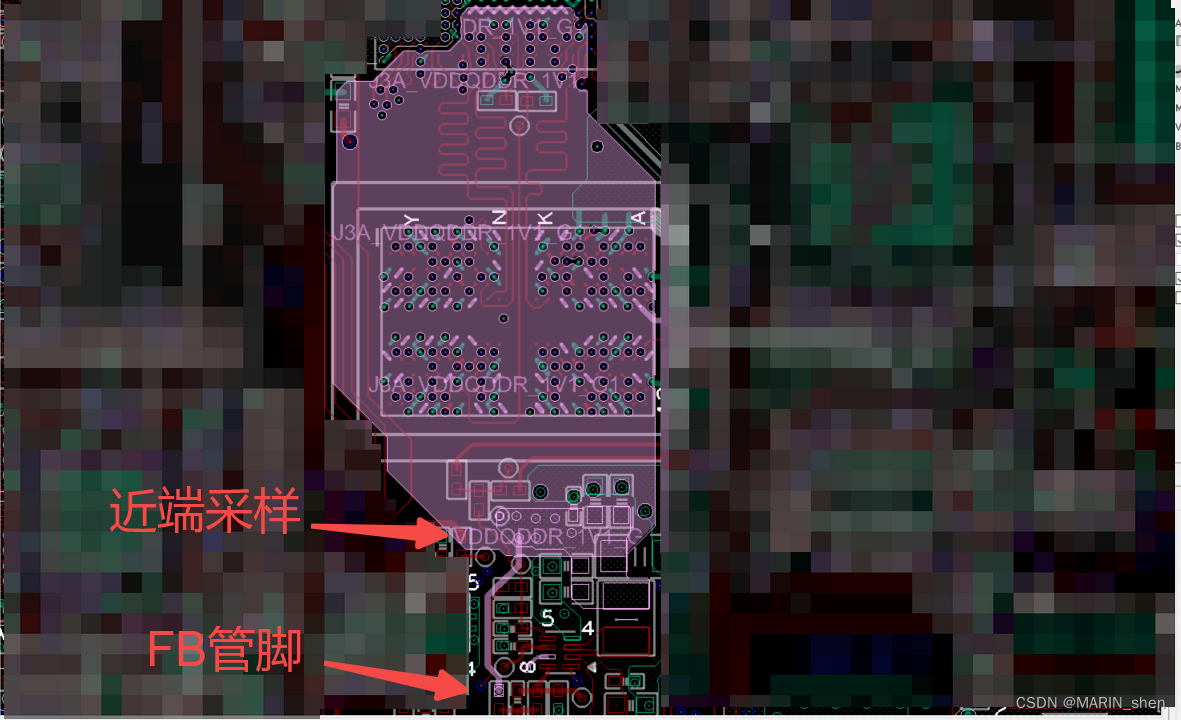

?A,改善前的设计如下图所示:

?

B, 改善后的设计如下图所示:

最后关于这个FB反馈点的走线有以下的几点需要大家注意一下:

1,走线宽度,这个远端反馈的走线尽量加粗到12-15MIL左右。

2,走线不要穿电感,晶振,开关管等比较敏感的器件。

3,FB的走线尽量短,直,不要绕来来去的。

4,与FB相连的分压电阻尽量靠近VAM端口放置。

以上就是本章的所有内容了,我们下篇文章不见不散。若有对这个直流压降仿真感兴趣的朋友们可以在评论区讨论分享一下不同的观点

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 国内外网络安全现状与存在的问题。应该如何缓解或解决这些问题

- 申请sectigo和certum的IP证书注意事项

- 项目启动后,页面新增修改数据显示-???

- 使用python netmiko模块批量配置Cisco、华为、H3C路由器交换机(支持 telnet 和 ssh 方式)

- 组合数问题

- 【华为OD机试真题2023C&D卷 JAVA&JS】分割均衡字符串

- 【Spring 篇】深入探讨MyBatis映射文件中的动态SQL

- 判断 Scanpy 的 AnnData 对象是否已经被对数化

- QMessageBox自定义按钮文本中文显示,按钮个数等

- arrow,一个神奇的 Python 库!