verilog语法基础-算术运算

发布时间:2023年12月17日

概述:

虽然算术运算的基本的计算,但是对于计算机器来说,是非常复杂的功能。FPGA能够进行算术运算仅仅是低位的整数运算。其中性能比较好的是加法运算,减法运算,乘法运算,和左移除法运算。其中加法运算和减法运算可以看成一种运算。本节主要讨论简单的算术运算结构。

verilog中算术运算符如下:

// The forllowing are the arithmetic operators as defined by the Verilog language.

//

// + .... Addition

// - .... Subtraction

// * .... Multiplication

// / .... Divide

// % .... Modulus

// ** ... Power Operator (i.e. 2**8 returns 256)

主要内容

1. 加法运算

2.减法运算

3.乘法运算

4.除法运算

5. 取模运算

6.幂运算

7. 左移除法运算

1. 加法运算

代码

module assign1(

input[3:0] a,b,

output y1,

output[4:0] y2

);

assign y1 = a[0]+b[0]; // 1位加法器

assign y2 = a+b; // 4为加法器

endmodule

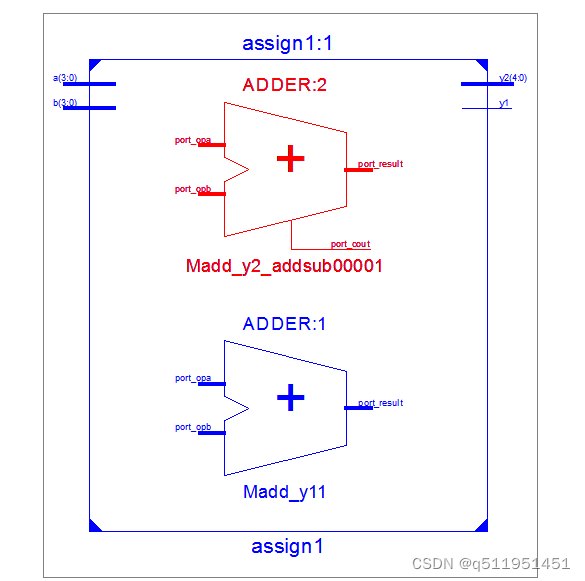

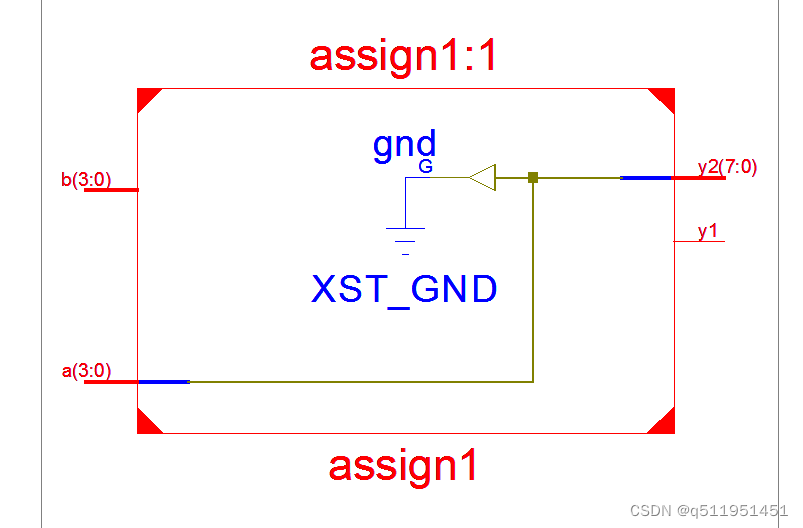

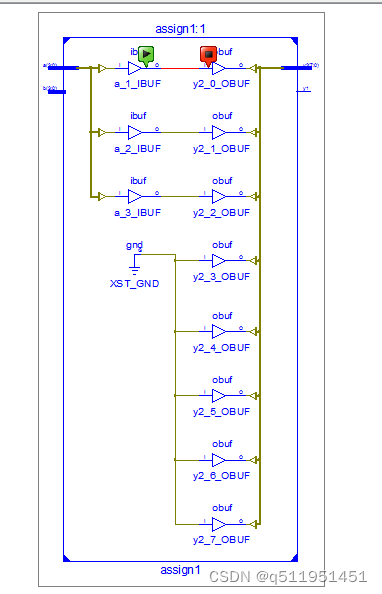

RTL结构图

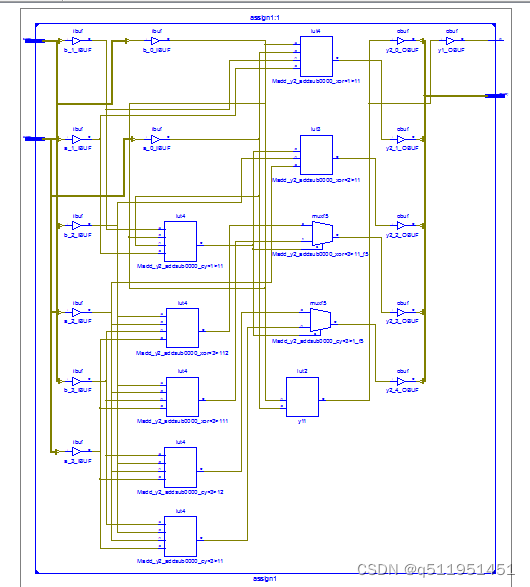

技术原理图

2. 减法电路

代码

module assign1(

input[3:0] a,b,

output y1,

output[3:0] y2

);

assign y2 = a-b; // 4为加法器

endmodule

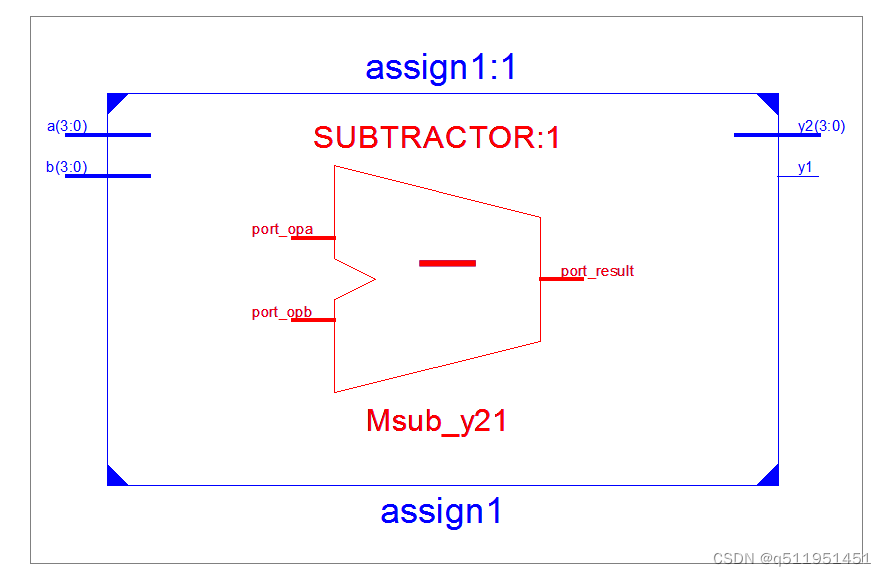

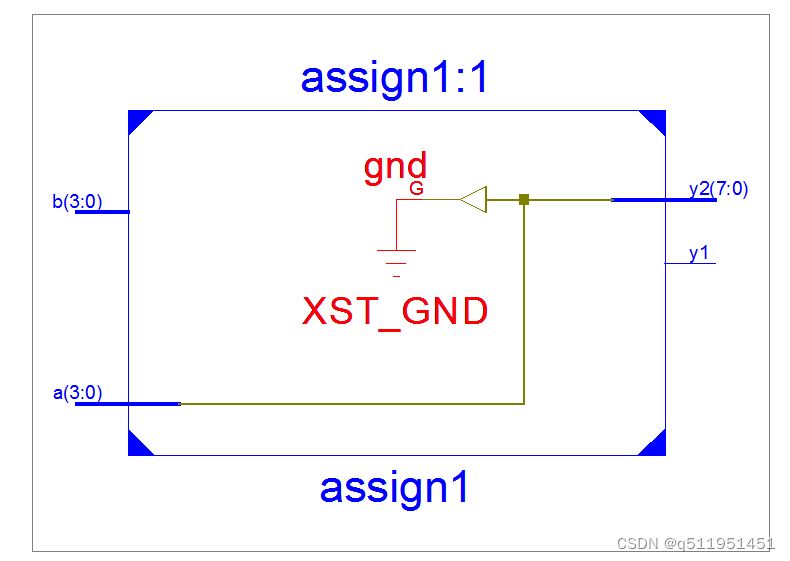

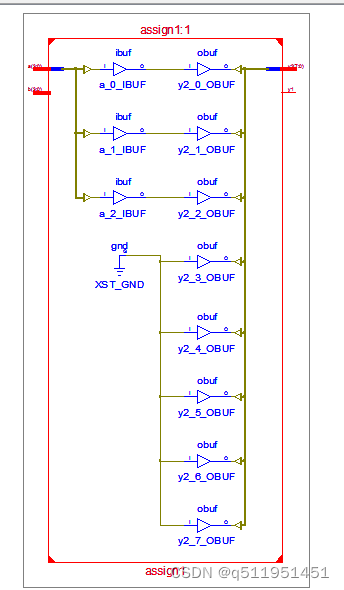

RTL结构图

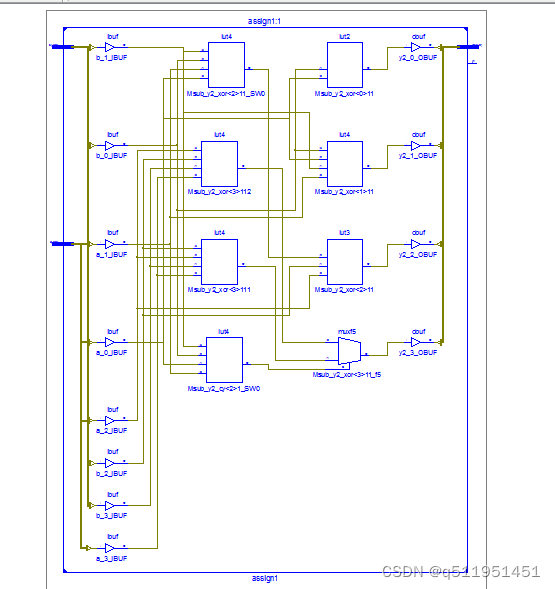

技术原理图

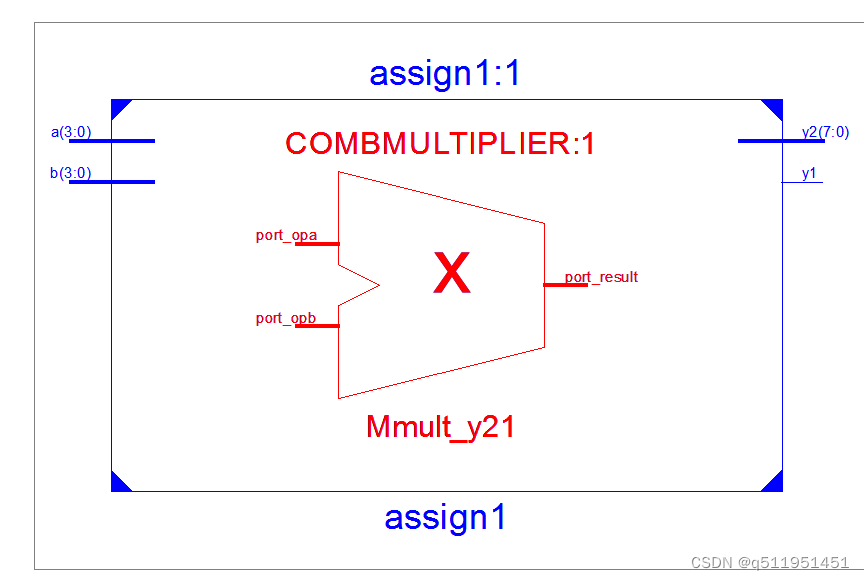

3.乘法电路

代码

module assign1(

input[3:0] a,b,

output y1,

output[7:0] y2

);

assign y2 = a*b; // 4为加法器

endmodule

RTL结构图

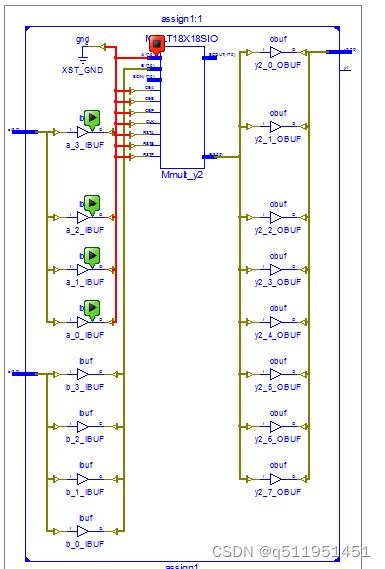

技术原理图,直接使用了18*18的专用乘法器,FPGA内部并没有直接自己重新构造乘法电路

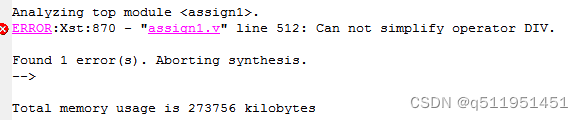

4. 除法电路

错误代码

module assign1(

input[3:0] a,b,

output y1,

output[7:0] y2

);

assign y2 = a/b;

endmodule

FPGA不能直接构造除法电路,否则报错

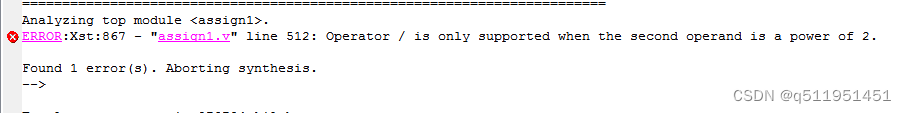

除以非2^n的数,都会报错

module assign1(

input[3:0] a,b,

output y1,

output[7:0] y2

);

assign y2 = a/3;

endmodule

报错结果

可用代码,只能除以2**n次方

module assign1(

input[3:0] a,b,

output y1,

output[7:0] y2

);

assign y2 = a/2; // 4为加法器

endmodule

RTL结构图,由此可知,就是重新布线

技术原理图

5. 取模运算

代码

// 34 取模运算

module assign1(

input[3:0] a,b,

output y1,

output[7:0] y2

);

assign y2 = a%8; // 4为加法器

endmodule

RTL结构图,取模运算也只支持2**n次方,他的原理就是只保留低位即可。

技术原理图

6. 幂运算**

代码

module assign1(

input[3:0] a,b,

output y1,

output[7:0] y2

);

assign y2 = 3**5; // 4为加法器

endmodule

幂运算仅仅支持常数运算,数值在软件上已经算好了,方便编程,并不会设计一个幂运算电路。

总结

1. FPGA自己自动构造的算术电路仅仅只有加法电路

2. 减法电路也是一种加发电路,

3. FPGA的乘法电路是通过调用专用乘法器来实现的,并不会在综合的过程自动构造乘法电路,乘法电路的资源取决于型号。

4. 除法和取模运算只支持2**n次方,并且只能进行常数运算,他用过连线的重新排布来实现

5. 幂预算只能是常数运算,软件直接计算结果,并不会构造具体电路,也不会对线的排布产生影响。主要是为了方便编程。

文章来源:https://blog.csdn.net/q511951451/article/details/134990068

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- ansible-playbook(剧本)

- 基于静态顺序表实现通讯录项目

- 一起玩儿物联网人工智能小车(ESP32)——26. 舵机的使用方法

- 【神经网络算子】

- SpringCloud+Consul快速开发示例

- 【论文解读】PV-RCNN: Point-Voxel Feature Set Abstraction for 3D Object Detection

- [算法基础 ~排序] Golang 实现

- Docker守护进程是什么

- 【C++】通过getline读取一行输入

- 【我与Java的成长记】之多态,重载与重写详解