FPGA开发设计

一、概述

FPGA是可编程逻辑器件的一种,本质上是一种高密度可编程逻辑器件。

FPGA的灵活性高、开发周期短、并行性高、具备可重构特性,是一种广泛应用的半定制电路。

FPGA的原理

采用基于SRAM工艺的查位表结构(LUT),LUT用于实现实际逻辑电路的功能,LUT本质上是一个RAM,事先将相应的结果存放于一个存储单元,输入信号进行逻辑计算就等于输入一个地址进行查表,将地址对应内容输入。

FPGA综合工具完成Verilog语言描述、逻辑网表到LUT实现的过程。即用户通过原理图或者HDL语言描述一个逻辑电路后,FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(结果)事先写入LUT的RAM中,EDA工具生成的烧进FPGA的bitstream文件。

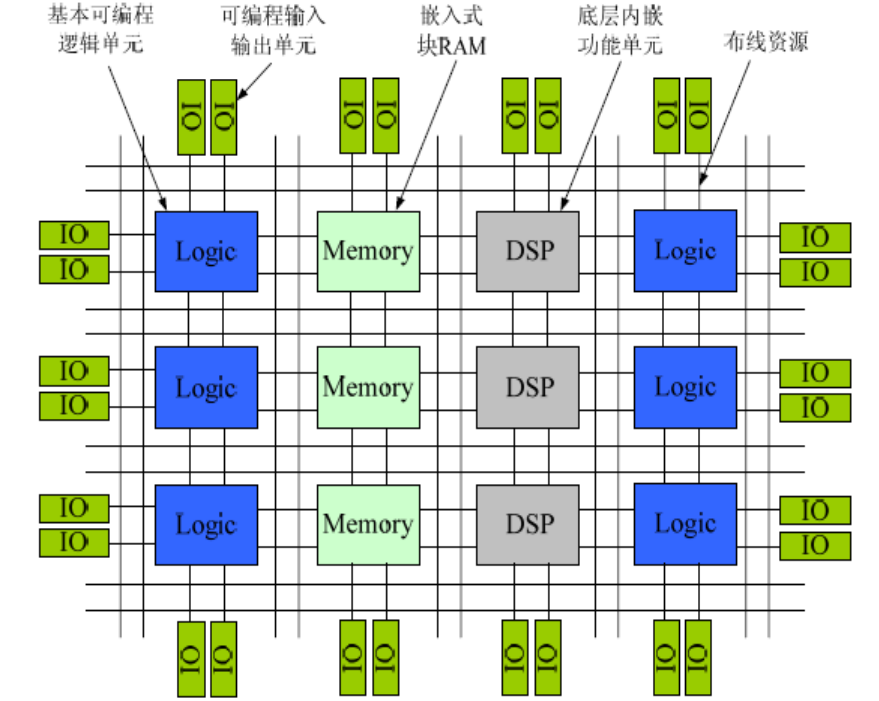

FPGA的结构

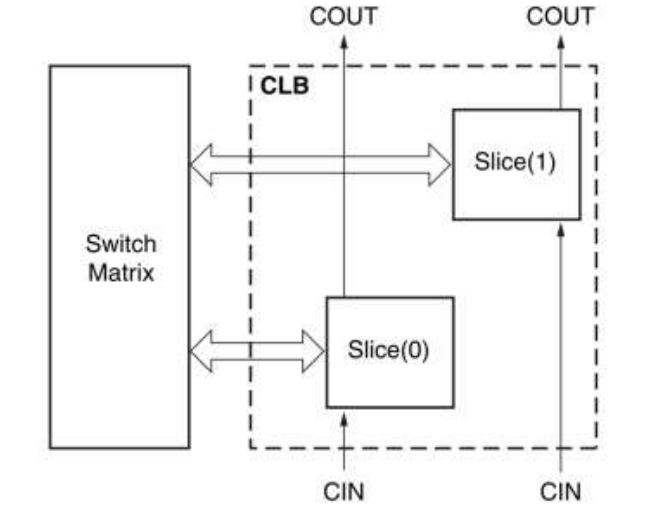

FPGA内部有多中部件,如DSP、Memory(BLOCK RAM/BLOCK ROM)、布线资源、可编程输入单元等,但最基本单元式CLB逻辑块,CLB的组成有查找表LUT,寄存器Flip-flop,多路选择器Mux。

CLB

LUT是FPGA用于实现组合逻辑电路的器件,具体作用是存储组合逻辑电路计算的所有结果通过LUT代替组合逻辑,而LUT中的值只和输入有关,因此FPGA中组合逻辑的功能由输入决定,不再和复杂度有关;LUT实现的组合逻辑的延迟是固定的

Mux

多路选择,配合LUT实现根据输入选择结果

FPGA中全局时钟资源

大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。与全局时钟资源相关的原语常用的与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM

IBUFG:输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。 IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和 SSTL等多种格式的IO标准。

IBUFGDS:IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。

BUFG:全局缓冲,它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。

BUFGCE:带有时钟使能端的全局缓冲。它有一个输入I、一个使能端CE和一个输出端O。只有当BUFGCE的使能端CE有效(高电平)时,BUFGCE才有输出。

BUFGMUX:全局时钟选择缓冲,它有I0和I1两个输入,一个控制端S,一个输出端O。当S为低电平时输出时钟为I0,反之为I1。需要指出的是BUFGMUX的应用十分灵活,I0和I1两个输入时钟甚至可以为异步关系

BUFGP:相当于IBUG加上BUFG。

BUFGDLL:全局缓冲延迟锁相环,相当于BUFG与DLL的结合。BUFGDLL在早期设计中经常使用,用以完成全局时钟的同步和驱动等功能。随着数字时钟管理单元(DCM)的日益完善,目前BUFGDLL的应用已经逐渐被DCM所取代。

DCM:数字时钟管理单元,主要完成时钟的同步、移相、分频、倍频和去抖动等。DCM与全局时钟有着密不可分的联系,为了达到最小的延迟和抖动,几乎所有的DCM应用都要使用全局缓冲资源。DCM可以用Xilinx ISE软件中的Architecture Wizard直接生成。

FPGA工作流程

逻辑设计验证 =》 综合 =》 实现 =》 编程与调试

综合

将高层次FPGA设计转化为逻辑链接网表的过程。

综合过程将会检查代码语法并分析设计层次结构,并针对用户选定的器件进行优化,综合结束产生硬件资源估算,但不一定准确

实现

通过翻译、映射、布局布线等过程将逻辑设计进一步转译为可以下载烧录到FPGA器件的特定物理文件格式的过程。

翻译过程是将所有的输入网表和约束条件组合成一个逻辑设计文件,这些信息被保存为NGD文件

映射是将带有逻辑原酸的整个电路划分为子块,一遍可以被装入到FPGA逻辑块中。该过程将NGD文件定义的逻辑适用于FPGA,并生成一个NCD文件。

布局布线是确定FPGA中逻辑单元的位置,确定单元间的连线。

二、Xilinx FPGA开发

Vivado使用

FPGA开发项目list

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 易点易动固定资产集成飞书,实现固定资产的一站式高效管理

- 2022年山东省职业院校技能大赛高职组云计算赛项试卷第一场-私有云

- TypeScript 从入门到进阶之基础篇(六) 类型(断言 、推论、别名)| 联合类型 | 交叉类型

- 银河麒麟桌面操作系统V10完成开机root用户登录

- Python下载安装

- 【Linux】进程信号

- 日志记录logging

- Vue3 开发实战分享——打印插件 Print.js 的使用(Vue3 + Nodejs + Print.js 实战)以及 el-table 与 el-pagination 的深入使用(下)

- 数字经济的不断发展,数字化转型已成为各行各业不可避免的趋势

- 5-Docker实例-nginx application