数字电子技术实验——ModelSim仿真教程

一、软件介绍

在进行数字电子技术实验时,时常需要对程序进行波形仿真。

此时可以使用ModelSim进行仿真。

该软件在安装Quartus时就同步安装了。(也可以在网上找资源下载安装)

本教程使用的ModelSim为安装QuartusⅡ18.1版本时携带的ModelSim。

1、在开始界面——win键点击所用应用

找到Intel FPGA 18.1.0.625 Lite Edition->ModelSim

2、直接去Quartus安装目录下找到modelsim_ase->win32aloem->modelsim.exe

二、基本仿真过程

1、激励文件Test Bench

在ModelSim仿真中,需要一个TestBench激励文件用于输入波形的设置。

1、创建Test Bench文件

1、直接新建一个.v文件或者.vt文件,从零开始编写。

2、通过Quartus生成一个文件模板。

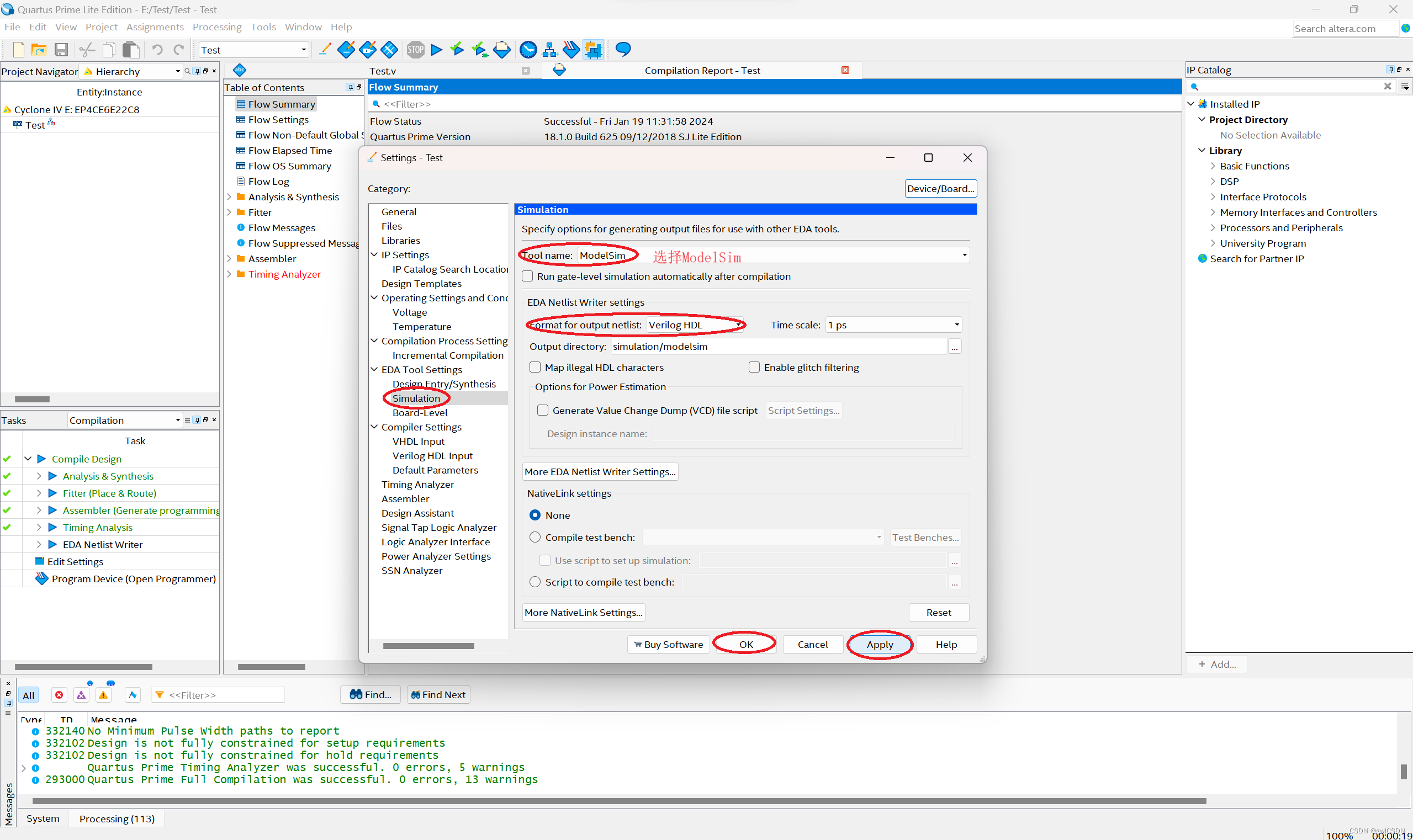

主页面工具栏Assignments->Setting

在Simulation中,设置仿真为ModelSim和Verilog HDL。点击Apply(应用) -> OK

重新编译通过后:工具栏Processing->Start->Start Test Bench Template Writer

就会生成一个激励文件模板,通过下方的文件路径可以找到该文件

可通过File->Open找到该文件并打开进行修改,也可以直接通过记事本等进行修改。

(可以删除注释掉的部分,以及那个reg eachvec;)

2、Test Bench文件介绍

需要注意第一行时间设置前面的符号(键盘左边Tab键上面一个键)

流程:时间设置->建立激励模块->调用程序主模块->输入波形设置

例:

2、项目建立

1、新建项目

主界面File->New->Project

填写项目路径和项目名,其余默认即可。

2、添加文件

添加以写好的文件到项目中:激励文件和程序文件。(自己建立的写有代码的.v和.vt文件,其余不需要)

1、直接点击Add Existing File

2、工具栏Project->Add to project->Existing File

3、鼠标右键->Add to Project->Existing File

可以将对应文件移到项目目录下,便于找到文件位置

选择对应的文件加入项目

3、编译和添加配置仿真

1、鼠标右键->Compile->Compile All

2、工具栏Compile->Compile All

编译通过后配置仿真

1、鼠标右键Add to Project->Simulation Configuration

2、工具栏Project->Add to project->Simulation Configuration

找到work(在新建项目填写项目路径和项目名时,图中第三行,默认的Library Name 是work)

选择激励文件中的模块(Test_vlg_tst)

因为此模块调用了主程序中的主模块,能包含到所有的模块,如果不选择该模块,则激励文件无法被使用。

双击即可进入仿真

3、开始仿真

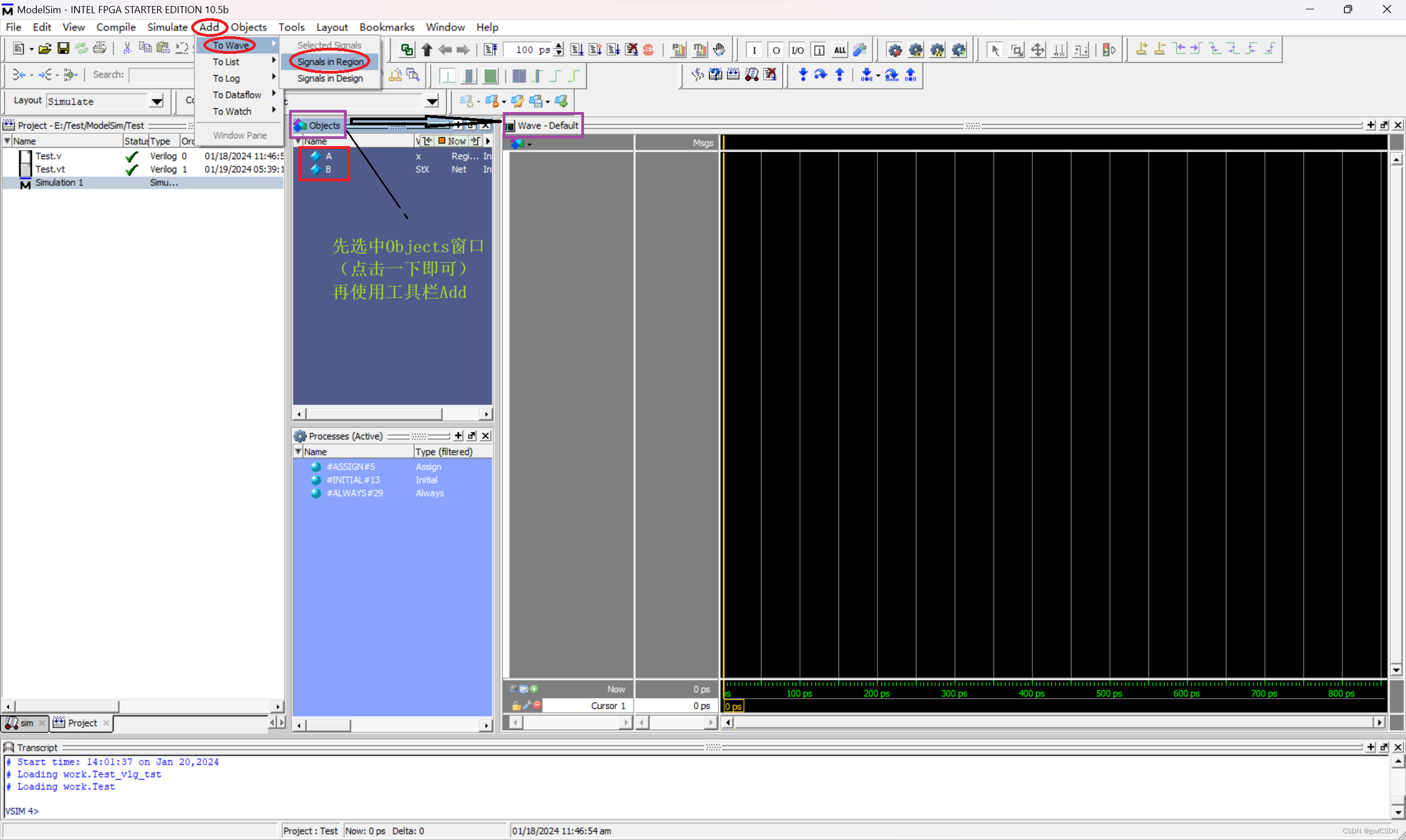

1、添加观察波形

需要将Objects窗口中的波(A,B)加入到Wave窗口,才能在Wave窗口观察到波形。

1、单击选中Objects窗口,工具栏Add->To Wave->Signals in Region,添加所有波到Wave中。

2、在Objects窗口,鼠标右键->Add to->Wave->Signals in Region,添加所有波。

也可以选中其中的某个波,再进行上述操作,选择Selected Signals,进行单个添加。

删除添加的波:在Wave窗口,选中某个波,鼠标右键->Edit->Delete即可删除。

2、选择仿真时长

在添加好需要观察的波后,就要选择仿真的时长。

1、可以设定时长进行运行仿真,生成一段波形。

2、可以一直运行仿真,不断生成波形。

可通过工具栏Simulation->Run选择;也可以直接点击对应按钮。

三、其他功能介绍

1、波形颜色调整

工具栏Tools->Edit Preferences打开颜色编辑器

左边第一栏选择Wave Windows调整波形窗口。

左边第二栏选择调整的目标,包括各种线条的颜色以及背景颜色等。

右边为效果展示区和颜色选择区。

黑白调色:上图第二栏黑色边框中调整为黑色,红色边框中调整为白色。效果如下:

左下角标尺的第一个按钮,可使左上方只显示波形名字。

2、标尺功能

左下角的加号可以增加标尺。

左下角标尺左边的小锁可以锁定标尺使其无法移动,同时使标尺线变为红色。

在选定一个波形和选定一个标尺后,可通过右上角的对齐按钮,使该标尺线对选定波形的上升沿或者下降沿,实现对齐效果。

在标尺上鼠标右键->Grid,Time......可调整标尺显示

可调整标尺显示的时间单位。

切换相邻两个标尺之间显示的信息为频率或者时间差。

温馨提示:

1、如果遇到报错,可以双击报错的信息以获取详细错误原因。

2、如果波形图中出现红线,可能是由于在程序文件代码编写时未给reg型变量赋初值。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!