数字IC笔试题——门控时钟与控制信号电平、与门门控、或门门控、上升沿门控、下降沿门控

????门控时钟问题。

(华为-2019-芯片-数字-34)

????从后端设计考虑,在必须使用门控时钟的时候,需要遵循一个原则:门控时钟的输出只能跟着时钟信号进行跳变,而不能跟着控制信号进行跳变,也就是说对于用NAND Gate或者AND Gate实现的门控时钟,控制信号只能在时钟的低电平处进行跳变;对于用OR Gate或者NOR Gate实现的门控时钟,控制信号只能在时钟的高电平处跳变()

A. 正确

B. 错误

答案:A

FPGA探索者

FPGA+数字IC笔试面试,无线通信物理层及数字信号处理,半导体芯片行业求职,校招社招实习,职场趣事,行业动态,打工人必备。

解析:

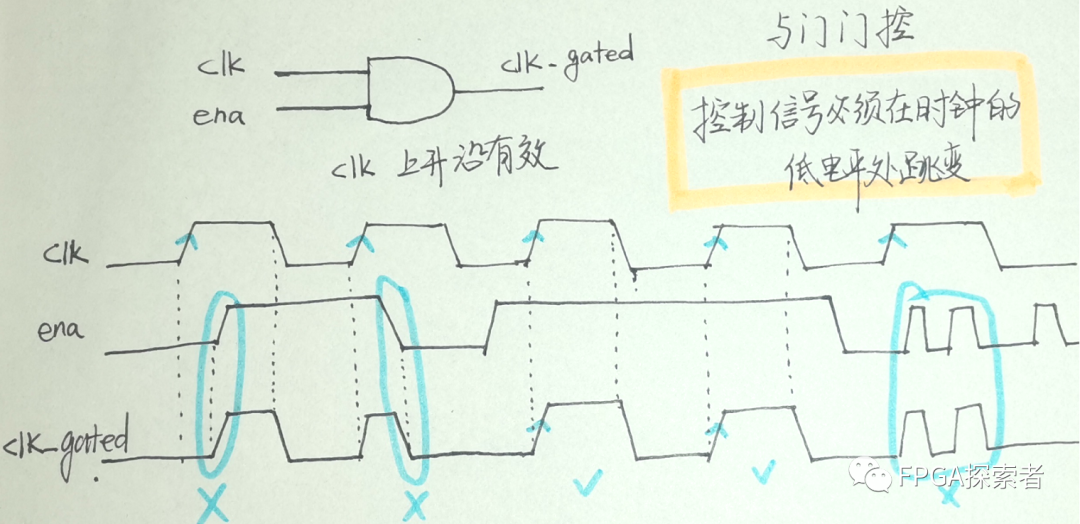

对于与门:

(1)使用条件:clk 上升沿有效;

(2)ena 高电平开启门控,ena 的电平跳变必须在时钟的低电平区间;

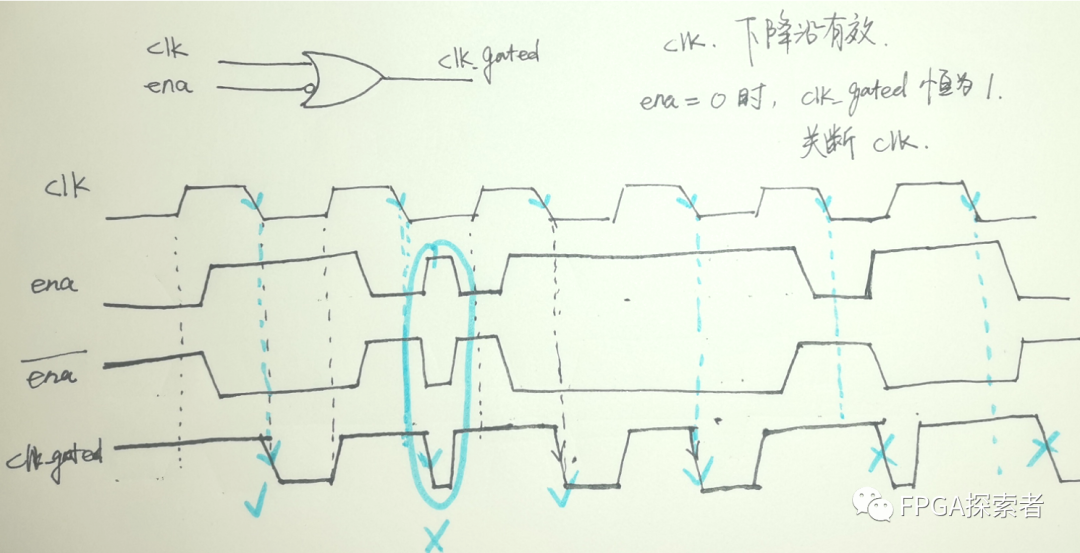

对于或门(ena 输入有个取非):

(1)使用条件:clk 下升沿有效;

(2)输入的 ena 高电平开启门控,ena 的电平跳变必须在时钟的高电平区间;

????如果或门上不对 ena 取非,则 ena 在低电平开启门控。

门控时钟:

????有效降低动态功耗,是低功耗设计方法之一,主要应用于低功耗设计领域。

????门控时钟在 ASIC 中使用较多,在 FPGA 使用较少,使用门控时钟会影响时序分析。

????对上升沿有效的 clk,使用与门进行门控,ena 使能信号跳变只能发生在时钟的低电平区;

????对下降沿有效的 clk,使用或门进行门控,ena 使能信号跳变只能发生在时钟的高电平区;

参考:

https://blog.csdn.net/bleauchat/article/details/96502907

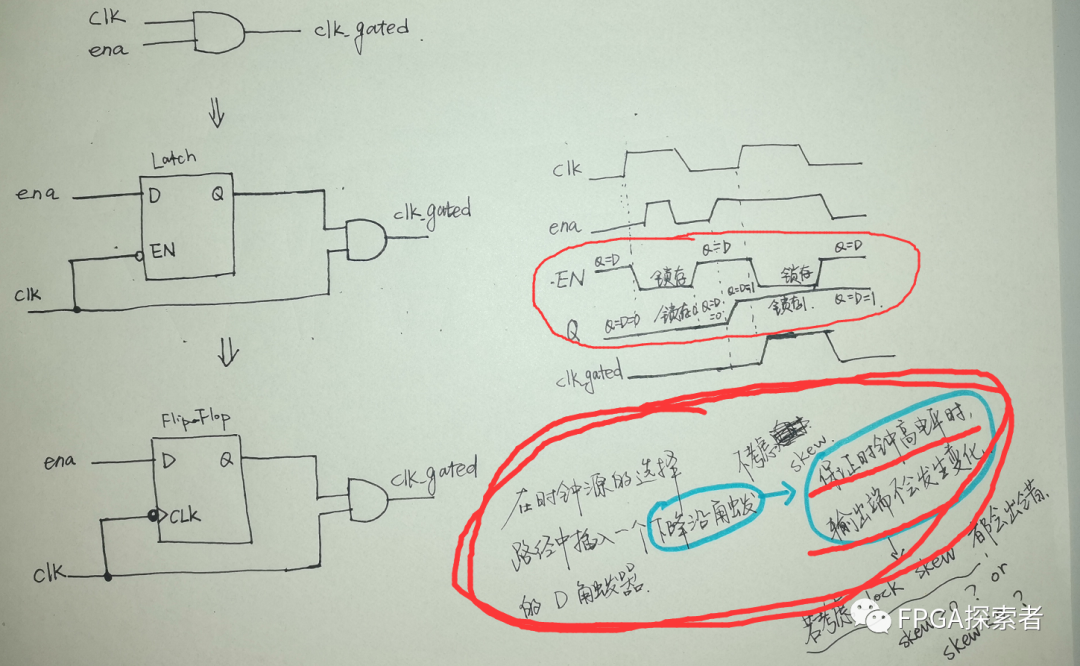

对上述单独的与门、或门组合逻辑的门控时钟的改进:

(1)使用锁存器

来源:

https://vlsi.pro/integrated-clock-gating-cell/

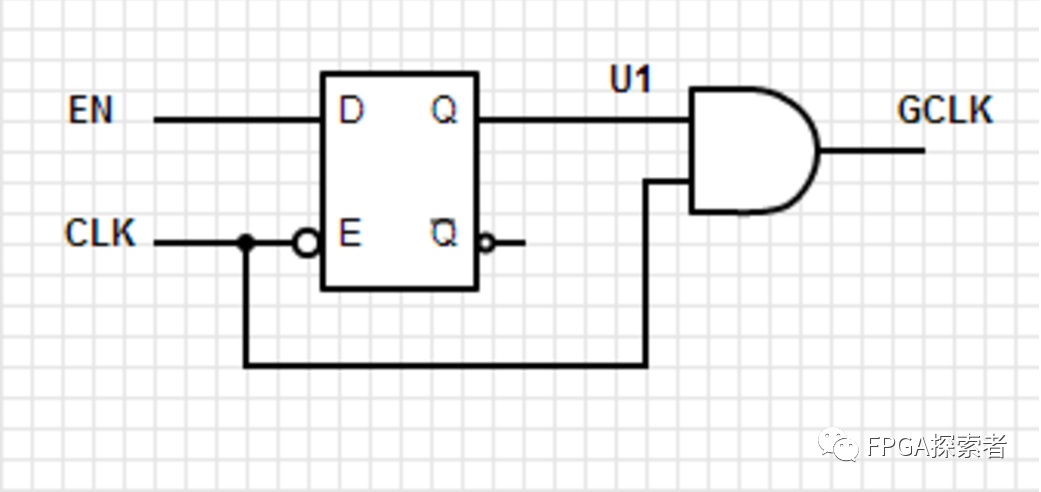

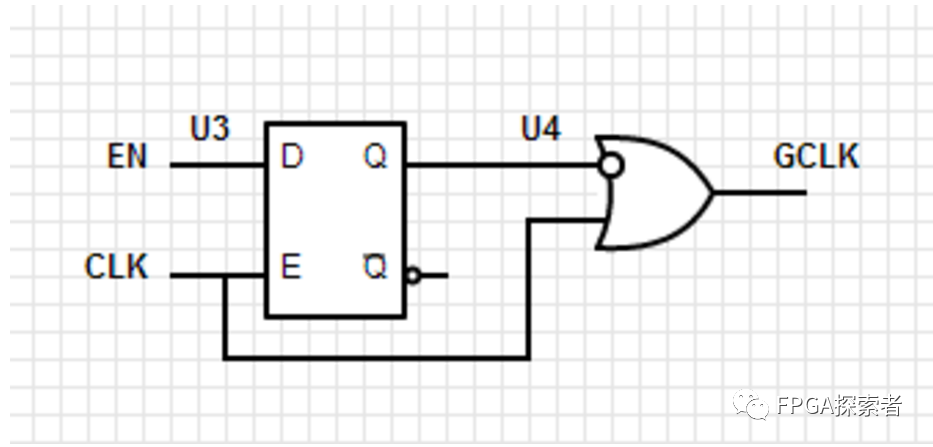

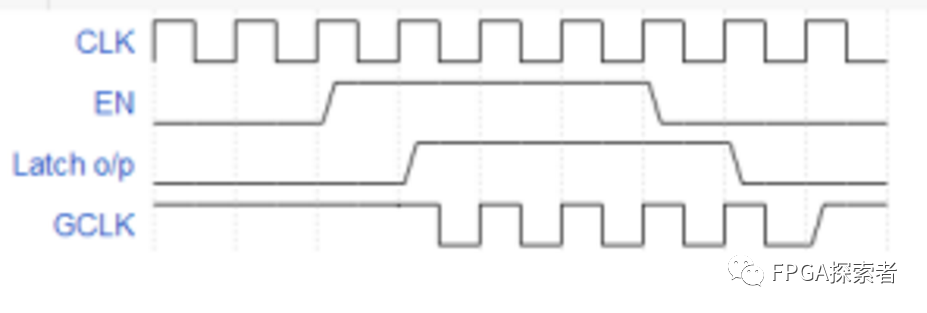

????对与门:

????使用一个锁存器,时钟 CLK 取反后作为使能端。

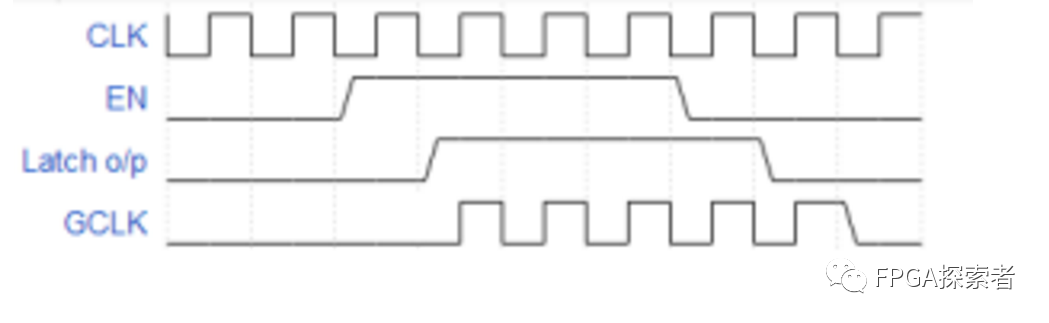

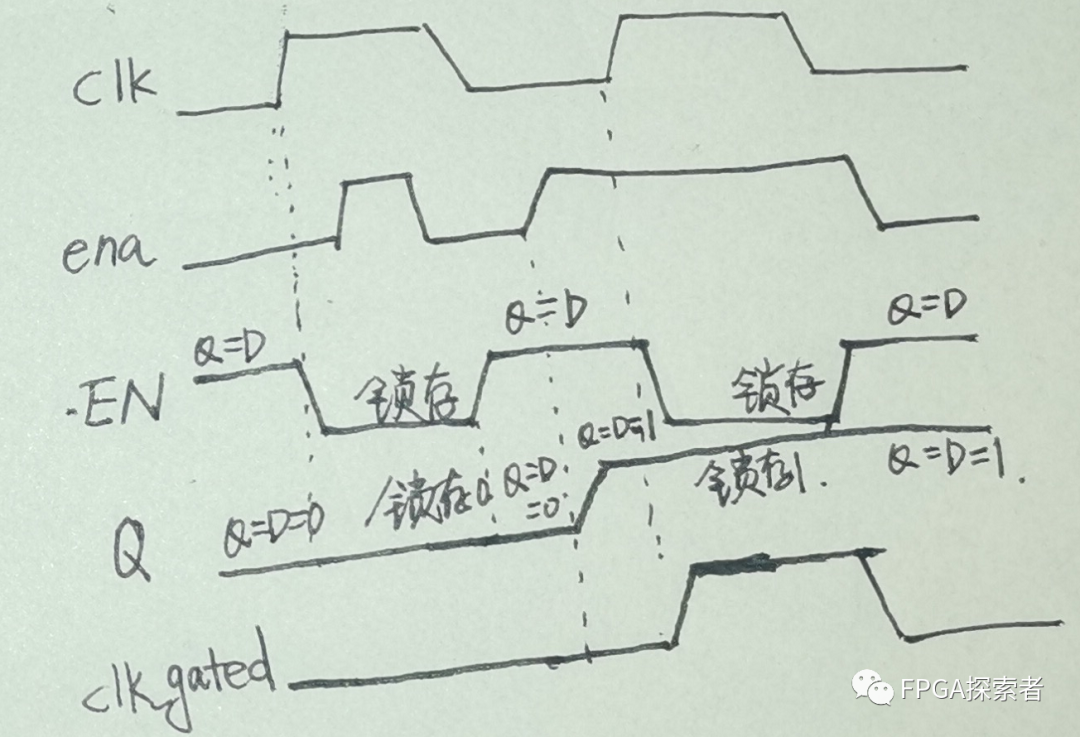

????对应时序波形:

????利用锁存器的锁存特性,得到时序图如下。

????对或门:

????使用一个锁存器,时钟 CLK 作为使能端。

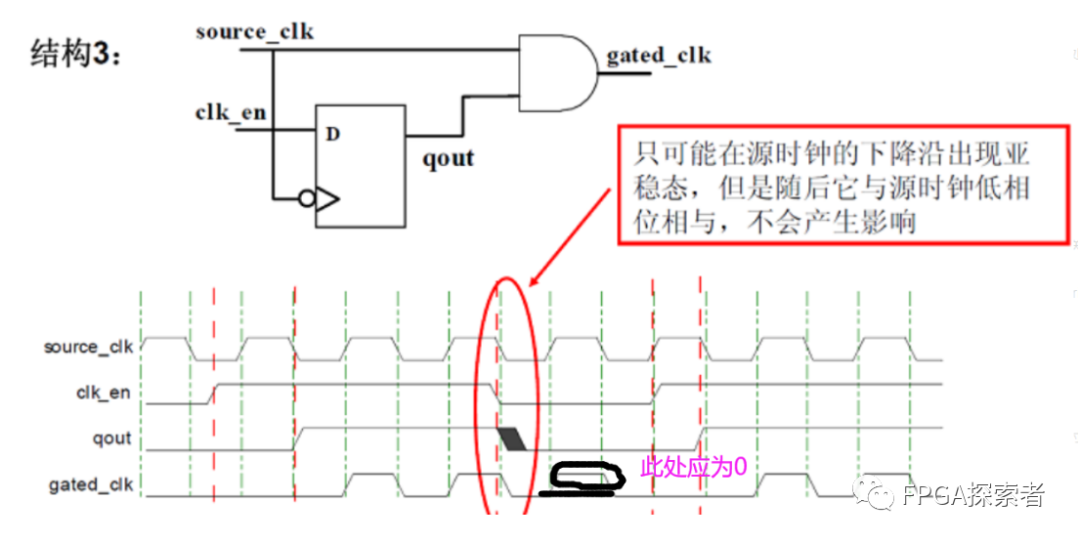

(2)使用触发器

????对与门,使用下降沿触发的 D 触发器寄存使能信号。

????使用下降沿的目的,保证时钟高电平时,输出端不会发生变化,跳变只出现在时钟的低电平区间。

????

????在不考虑时钟 skew 的情况下,如下图所示。

????要不要考虑 clock skew?使用 ICG 集成门控的库或者原语,应该是不需要考虑的(如果要使用门控时钟,也只能用库或者原语,自己写的还是别用了)。

????如果考虑 skew 的话,上升沿触发和下降沿触发,对应 skew?正负 2 种情况下,各有 1 种会出现毛刺,感兴趣的可以自己画一画。

时序、跨时钟域、格雷码、关键路径、STA 静态时序分析:

CDC跨时钟域处理及相应的时序约束【set_clock_groups】【set_max_delay】【FPGA探索者】

FPGA时序分析之关键路径(Critical Path)【华为静态时序分析资料】【笔试面试】

FPGA中亚稳态【Tsu建立时间】【Th保持时间】【Tmet决断时间】【recovery恢复时间】【removal移除时间】

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- launch4j 使用:将Java应用程序转成Windows本地可执行文件 (.exe)

- 使用Web自动化测试工具显著好处

- windos exe 以服务的形式运行(开机运行)

- [算法与数据结构][c++][python]:C++与Python中的赋值、浅拷贝与深拷贝

- 2024年【安全员-B证】试题及解析及安全员-B证模拟试题

- Gateway No servers available for service

- VX小程序Burp抓包

- js for和forEach 跳出循环 替代方案

- Elasticsearch入门

- vue总结