vivado 创建编译后工程

创建后期合成项目

合成后项目以合成网表、完全生成的块设计、完全生成的IP以及相应的约束。然后,您可以分析、布局和实施设计

注意:您可以使用XST或第三方合成工具来创建合成网表。

重要!使用EDIF和NGC文件时,顶部单元格名称必须与文件名称相匹配。

1.按照创建项目中的步骤进行操作。

2.在“项目类型”页面中,选择“后期合成项目”,然后单击“下一步”。

注意:如有必要,您可以选择此时不指定来源。这将跳过添加的步骤设计源,使您能够选择目标零件并创建项目。

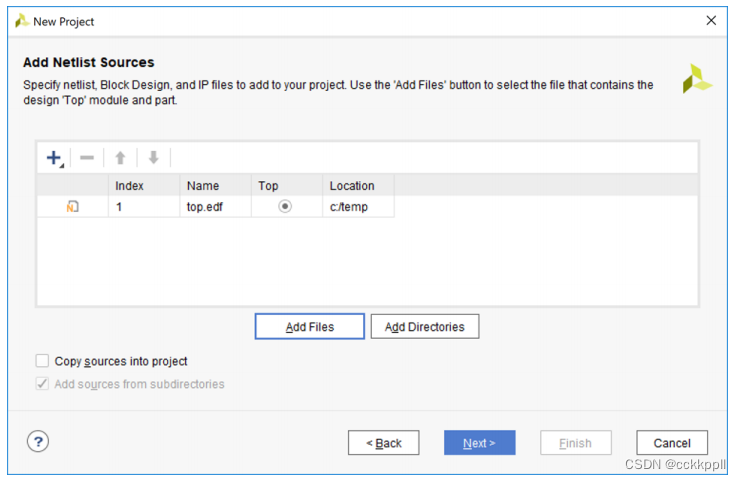

3.在“添加网表源”页面中,使用以下选项指定要读取的网表文件,识别包含顶级模块的文件,并定义要搜索的较低级别的目录模块网表,然后单击下一步。

?添加文件:调用文件浏览器,以便您可以选择网表文件(结构化Verilog,SystemVerilog、EDIF或NGC)、BD文件和XCI文件(IP的所有输出产品必须生成,包括DCP),或设计检查点文件(DCP)添加到项目

建议:始终使用XCI文件参考IP。始终参考块设计使用BD文件;不建议只读取IP或BD DCP文件。而DCP会包含约束,它不提供IP或BD可以提供的其他输出产品,并且可能需要的,例如ELF、COE和Tcl脚本。

注意:为包含顶级网表的文件启用“顶部”单选按钮。

?添加目录:调用目录浏览器,以便您可以选择要搜索的目录模块。指定目录中具有有效源文件扩展名的文件将添加到项目

?删除:该按钮从列表中删除选定的源文件和目录。

?上移/下移:按列表顺序上移/下移文件或目录。的顺序文件会影响处理顺序。

?将源复制到项目中:将文件复制到本地项目目录中,而不是引用原始文件。如果使用“添加目录”添加源文件的目录,将文件本地复制到项目中时,将维护目录结构。对于有关详细信息,请参阅使用远程源或将源复制到项目中。

?从子目录添加源:在目录的子目录中查找网表文件使用Add Directories指定。

4.可选:在“添加约束”页面中,设置以下选项,然后单击“下一步”:

?添加文件:调用文件浏览器,以便选择要添加到项目中的SDC或XDC文件。

?创建文件:为项目创建一个新的顶级XDC文件。

?删除:从约束列表中删除选定的文件。

?上移/下移:按列出的顺序向上或向下移动约束文件。命令依赖于订单;约束的最后一个读取命令覆盖的效果早期命令。

?将约束复制到项目中:将约束文件复制到本地项目目录中而不是引用原始文件。

注意:在与RTL或网表源文件关联的相同目录中找到的任何SDC或XDC文件将自动列为要添加到项目中的约束文件。

5.在Default Part(默认零件)页面中,选择AMD零件或TDP板,然后单击Next(下一步):

?部件:列出可用的设备。有关设备资源的信息显示在表中看法您可以使用“产品类别”、“族”、“子族”、包、速度来过滤列表等级和温度等级过滤器。您也可以使用“搜索”字段来查找特定的设备。

?板:列出可用的TDP板以及板上使用的AMD部件。信息关于表视图中显示的设备资源,例如I/O引脚数、LUT数量和触发器以及可用的块RAM。您可以使用供应商、显示来筛选列表名称和Board Rev过滤器。您也可以使用“搜索”字段来查找特定的电路板零件。

6.在“新建项目摘要”页面中,查看定义项目的选定选项,以及单击“完成”。

创建I/O规划项目

您可以将I/O规划项目用于设备探索和规划的设备引脚输出正在进行的系统级设计。您可以在完成之前创建此类型的项目HDL或合成的网表。例如,这允许您与交换设计信息系统级或PCB设计者。有关I/O规划的更多信息,请参阅VivadoDesign Suite用户指南:I/O和时钟规划(UG899)。

1.按照创建项目中的步骤进行操作。

2.在“项目类型”页面中,选择“I/O规划项目”,然后单击“下一步”。

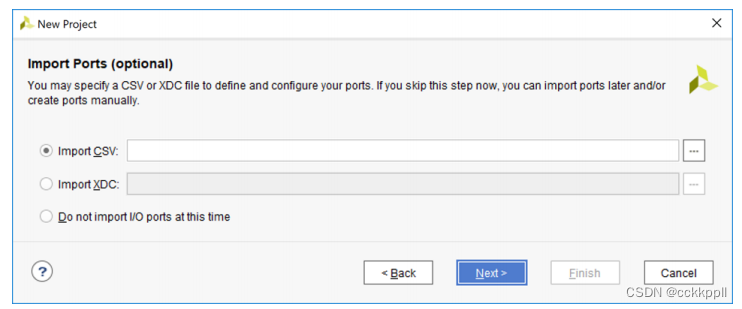

3.可选:在“导入端口”对话框中,使用以下选项为选择文件导入I/O端口定义和约束,然后单击“下一步”。

?导入CSV:选择具有I/O端口定义的CSV文件。有关CSV的更多信息文件,请参阅Vivado Design Suite用户指南:I/O和时钟规划(UG899)。

?导入XDC:仅选择具有I/O端口相关约束的XDC。

?此时不导入I/O端口:创建一个空项目。您可以创建或导入I/O稍后。

注:使用RTL项目可以使用RTL头文件或源文件对设计执行I/O引脚规划。

4.在Default Part(默认零件)页面中,选择AMD零件或TDP板,然后单击Next(下一步):

?部件:列出可用的设备。有关设备资源的信息显示在表中看法您可以使用“产品类别”、“族”、“子族”、包、速度来过滤列表等级和温度等级过滤器。您还可以使用“搜索”字段查找特定设备

?板:列出可用的TDP板以及板上使用的AMD部件。信息关于表视图中显示的设备资源,例如I/O引脚数、LUT数量和触发器以及可用的块RAM。您可以使用供应商、显示来筛选列表名称和Board Rev过滤器。您也可以使用“搜索”字段来查找特定的电路板零件。

5.在“新建项目摘要”页面中,查看您选择的用于定义项目的选项,以及单击“完成”创建并打开项目。

注:有关内存IP I/O规划的更多信息,请参阅Vivado Design Suite用户指南:I/O和时钟规划(UG899)。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 安科瑞汽车充电桩在西北地区的应用——安科瑞 顾烊宇

- 美易平台:花旗策略师看好美股前景,预测标普500指数年底冲刺5100点

- AUTOSAR从入门到精通-Autosar 中断机制(七)

- Vue.js 3.4版本发布:解析速度提升2倍,双向绑定革新等新功能

- 解决ElementUI导航栏中的vue-router在3.0版本以上重复点菜单报错问题

- Python在Web开发中的最佳实践与经验总结

- 【路由】基于Matlab实现LEACH(低能耗自适应集群层次路由)和 DEEC(分布式能量高效集群)路由算法

- 【PS】PS设计图欣赏、学习、借鉴

- webgl调试之排查内存泄漏

- 二级市场买入 ETF 能救市吗?深入了解 ETF 对股市的影响