Triumphcore FPGA调测试记录

发布时间:2024年01月10日

FPGA采用Xilinx pynq Z2开发板。基于V2.5版本开发

- 2024.1.7

复位状态导致取指时序错误

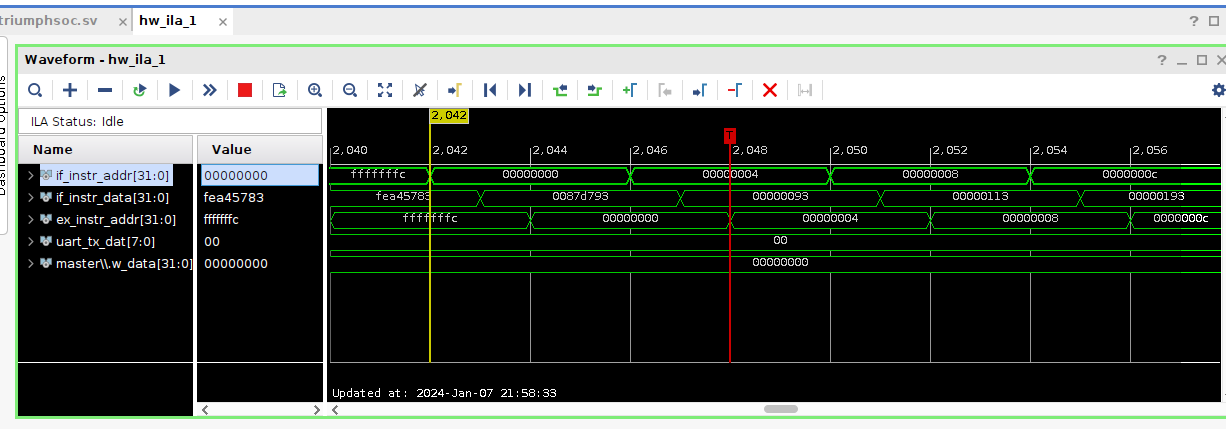

错误波形:

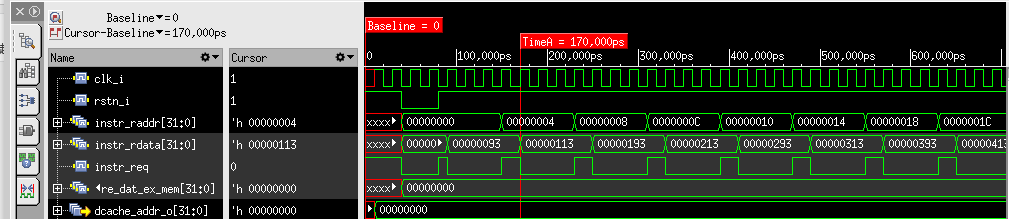

正确波形

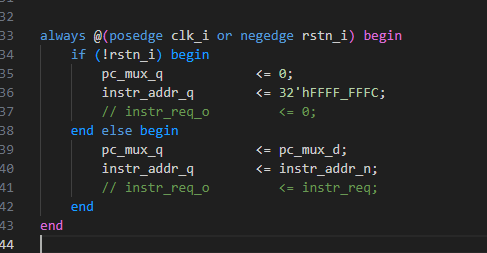

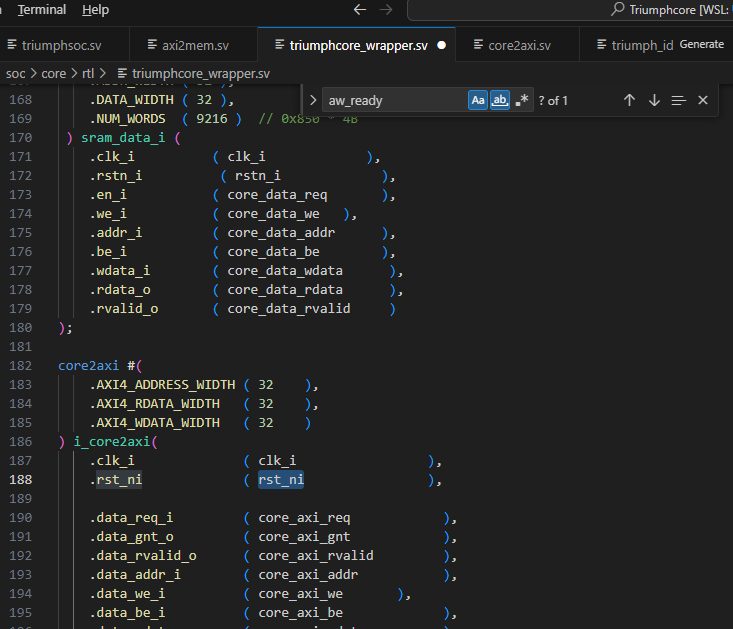

问题代码:

- 2024.1.9

clock_wizard设置输入时钟是输出时钟的2^n倍,输出时钟的占空比才是50%

即使clock_wizard设置占空比是50%,如果不是2^n倍,实际占空比也不会是50%,甚至也会影响其他信号的占空比。

- 2024.1.10

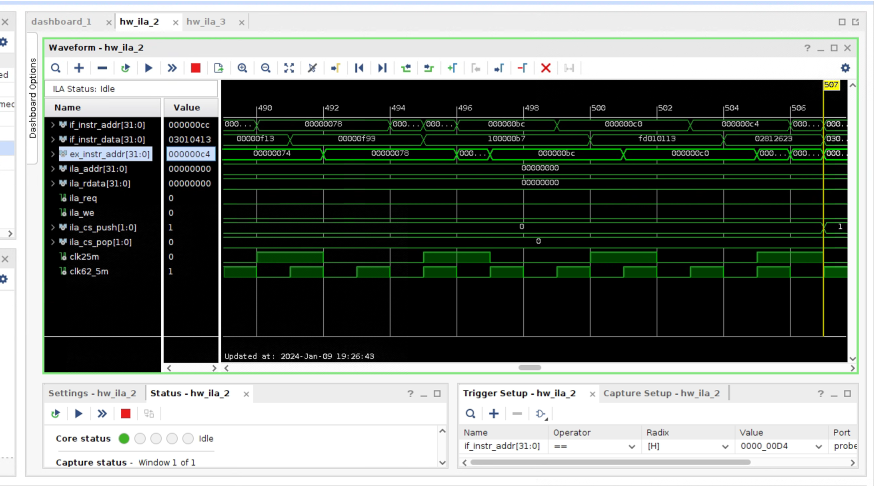

复位信号赋值错误导致core2axi中状态机CS始终不变化

w_valid只拉高一个周期,拉了很多波形出来,本来以为是aw_ready_i的组合逻辑路径较长,FPGA综合时序的问题,结果发现aw_ready_i在和aw_ready同一cycle拉高,然后就想到状态机未跳转的问题,结果一来出来发现NS变化,CS不变,那就是时钟和复位的问题了,时钟不太可能有问题,那就是复位的问题,然后一看代码,傻眼了。。

欸,改吧改吧。

后来想,为啥软仿没查出来呢?

软仿复位信号是Z,没有下降沿触发,CS默认也是0。

文章来源:https://blog.csdn.net/qq_39815222/article/details/135498096

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Python 算法交易实验67 第一次迭代总结

- Intel开发环境Quartus、Eclipse与WSL的安装

- 大模型学习与实践笔记(四)

- MATLAB | 圣诞节快到了,一起画两款动态圣诞树吧~

- 视频智能识别周界入侵检测AI智能分析网关V4如何配置ONVIF摄像机接入

- 四、java基础—流程控制

- CVE-2023-37582 Apache RocketMQ NameServer远程代码执行漏洞

- 【数据结构】并查集的简单实现,合并,查找(C++)

- Wargames与bash知识11

- 表单验证开发 - 登录注册开发(3)