SV接口的驱动和采样_2023.12.27】

发布时间:2023年12月29日

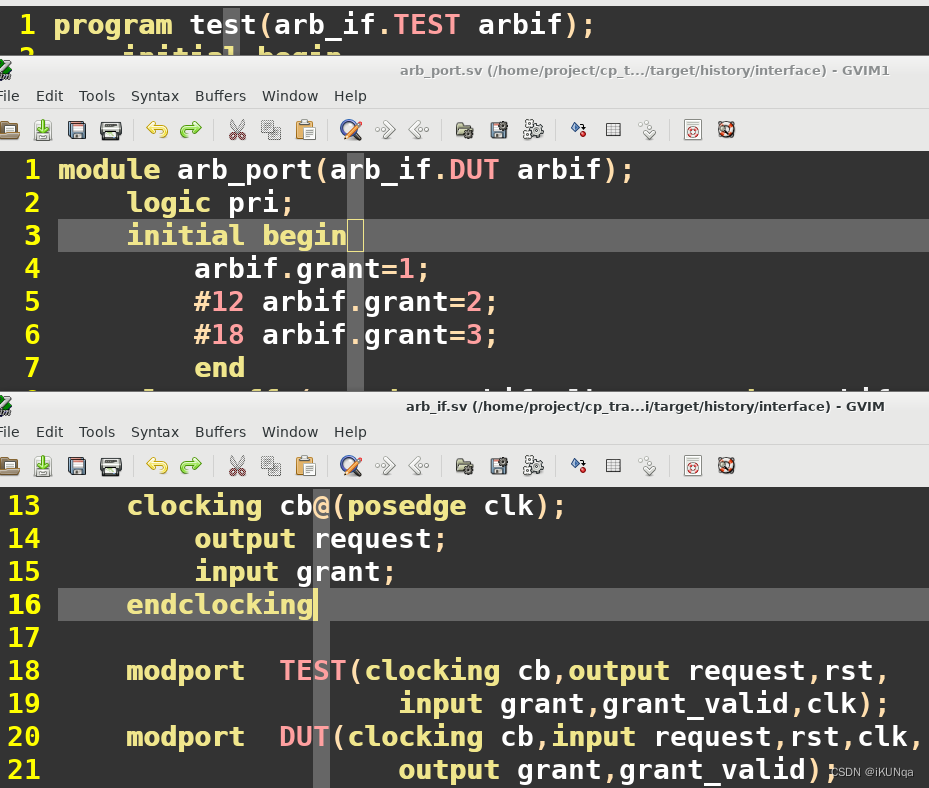

cb

使用cloking block进行信号的同步

在cloking block,所有信号的采样和驱动,都是和时钟同步的

clocking cb @(posedge clk);

input grant;

output request;

endclocking

接口同步

用@和wait来同步测试平台中的信号

@bus.cb;

接口信号采样与驱动

采样沿之前的值,驱动沿之后的值

cb中input可读不可写,dut的信号影响cb的相应信号

output可写不可读,cb的信号影响dut的相应信号,读dut的信号

cb中output信号赋值驱动必须要用非阻塞赋值

在cb中,采样(input)和驱动(output):

同步后的采样信号,都是前一状态的值

同步后的驱动信号,都是当前状态的值

默认输入偏差为1step,输出偏差为#0

改变默认的方法:cb中加default input #2 output #2;

接口中的双向信号

logic不能被inout驱动

SV中没有明确定义如何驱动接口中的异步双向信号,故使用的方式:

连续赋值语句assign

虚接口

program中不支持always块

cb的使用

引用信号写为arbif_DUT.grant

文章来源:https://blog.csdn.net/xiaotong121/article/details/135251847

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章