SPI接口协议

SPI接口协议

????????SPI(Serial Peripheral Interface)是由Motorola公司定义的接口协议标准,串行外设接口(SPI)是微控制器和外围IC(如传感器、 ADC、 DAC、移位寄存器、 SRAM等)之间使用最广泛的接口之一。SPI是一种同步、全双工、主从式接口,来自主机或从机的数据在时钟上升沿或下降沿同步,主机和从机可以同时传输数据, SPI接口可以是3线式或4线式。

一、SPI接口协议简介

????????串行外设接口 (SPI) 总线是一个工作在全双工模式下的同步串行数据链路。它可用于在单个主控制器和一个或多个从设备之间交换数据。其简单的实施方案只使用四条支持数据与控制的信号线。

????????1、接口定义:

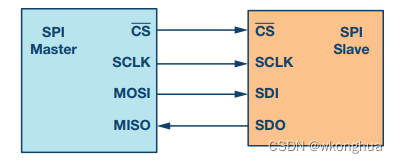

????????4线SPI接口信号:

????????虽然SPI接口协议标准已经是事实上的标准,但它并非官方法律上的标准,因此不同的厂家的集成电路SPI端口名称经常不同,但通常含义相同:

????????(1)时钟(CLK, SCLK,SCK,and so on...)

????????(2)片选(CS,SS,NSS,and so on...)

????????(3)主机输出、从机输入(MOSI,DO,and so on...)

????????(4)主机输入、从机输出(MISO,DI,and so on...)

图 1 基本的四线SPI总线接口

????????产生时钟信号的器件称为主机,主机和从机之间传输的数据与主机产生的时钟同步。同I2C接口相比, SPI器件支持更高的时钟频率。用户可以查阅产品数据手册以了解SPI接口的时钟频率规格。SPI接口只能有一个主机,但可以有一个或多个从机。图1显示了主机和从机之间的SPI连接。

????????来自主机的片选信号用于选择从机。这通常是一个低电平有效信号,拉高时从机与SPI总线断开连接。当使用多个从机时,主机需要为每个从机提供单独的片选信号。本文中的片选信号始终是低电平有效信号,也有部分厂家器件的SPI接口片选信号支持高电平有效,用户需根据产品数据手册使用。

????????MOSI和MISO是数据线, MOSI将数据从主机发送到从机, MISO将数据从从机发送到主机。如AD5683RBRMZ-3,此类器件的SPI接口SDI/SDO仅支持输入/输出,均为单向接口。也有部分器件的4线SPI接口中MISO(SDI)输入接口可以配置为双向接口(SDIO),针对此类器件可以通过配置器件相关寄存器使用4线通信,也可以根据需要配置为3线通信。

????????3线SPI接口信号:

????????有时候主从器件在信号传输时只需要三根线,例如:

????????(1)从机器件SPI接口有3个信号线:部分DAC器件可能没有必要回读数据或者仅需要对ADC发送数据,在这种场景下器件的SPI接口被定义为3线接口(此时器件仅支持三线SPI:SCLK/CS/MISO(SDI),只有三根线),其中MISO(SDI)仅作为输入接口,如AD5683RBRMZ。

图2 从机三线SPI接口,SDI单向

????????(2)从机器件SPI接口有3个信号线:器件支持SPI读写,SPI物理接口由三根线组成(此时器件仅支持三线SPI:SCLK/CS/SDIO,只有三根线),其中SDIO作为输入/输出双向接口,可写可读,如AD9629BCPZ-40。

图3 从机三线SPI接口,SDIO双向

????????(3)从机器件SPI接口有4个信号线(SCLK/CS/MOSI/MISO,参考图1),但是器件可根据需要配置为四线或三线通信。一般情况下器件默认为4线通信,配置为四线通信时通过对相关寄存器特定bit位写入相关值实现,主机的MOSI和MISO分别接从机器件的MISO和MOSI,支持全双工双向通信;当配置为三线通信时,通过对相关寄存器特定bit位写入相关值实现三线通信,此时从机MOSI(SDO)为高阻态,MISO(SDI)配置为双向通信SDIO,通过从机SDIO写入数据时,接口时序和四线SPI接口时序相同,通过从机SDIO读出数据时,在写入要读的地址后,对应地址的数据,本应通过MOSI(SDO)输出,此时数据输出顺序移位到SDIO接口上输出。可参考AD9361/AD6676/AD9163等器件的手册。

图4 从机四线SPI接口,SDIO双向

????????2、数据传输:

????????SPI 数据速率一般在 1 到 70MHz 的范围内,字长原则上可以根据需要定义任意多bit的字长(例如7bit,9bit and so on...),但通常主从机SPI的字长为从 8 位及 12 位到这两个值的倍数,在使用时可根据数据手册中的参数灵活配置。

????????要开始SPI通信,主机必须发送时钟信号,并通过使能CS信号选择从机。片选通常是低电平有效信号,因此,主机必须在该信号上发送逻辑0以选择从机。 SPI是全双工接口,主机和从机可以分别通过MOSI和MISO线路同时发送数据。在SPI通信期间,数据的发送(串行移出到MOSI/SDO总线上)和接收(采样或读入总线(MISO/SDI)上的数据)同时进行,在串行时钟沿同步数据的移位和采样。 SPI接口允许用户灵活选择时钟的上升沿或下降沿来采样和/或移位数据。

????????SPI通信包括四种不同的模式,模式取决于时钟极性CPOL(polarity)和启动数据传输时(CS拉低)的采样边沿,即相位CPHA(phase),根据配置时钟极性(CPOL)和相位(CPHA)的不同,可实现时钟信号 180 度的相移以及半个时钟周期的数据延迟移位输出和采样。

????????时钟极性是指时钟线空闲时的状态,相位是指设备从数据线采样的时刻,组合如下:

图5 CPOL/CPHA不同组合表示含义

图6 CPOL/CPHA不同组合时的时钟采样边沿

????????SPI模式通过CPOL和CPHA决定:

图7 SPI不同模式说明

图8 SPI接口CPOL/CPHA对应的时序图

????????不同模式下,SPI数据传输时序图如下图所示:

????????(1)Mode 0: CPOL = 0,CPHA = 0,数据在CS有效时CLK的第一个时钟沿(上升沿)采样读取,在下降沿移位输出(变化)。

图9 SPI Mode 0时序图

????????(2)Mode 1: CPOL = 0,CPHA = 1,数据在CS有效时CLK的第二个时钟沿(下降沿)采样读取,在上升沿移位输出(变化)。

图10 SPI Mode 1时序图

????????(3)Mode 2: CPOL = 1,CPHA = 0,数据在CS有效时CLK的第一个时钟沿(下降沿)采样读取,在上升沿移位输出(变化)。

图11 SPI Mode 2时序图

????????(4)Mode 3: CPOL = 1,CPHA = 1,数据在CS有效时CLK的第二个时钟沿(上升沿)采样读取,在上升沿移位输出(变化)。

图12 SPI Mode 3时序图

????????上图(图9~图12时序图)中,在传输协议上,MSB为一帧数据bit中第一个采样时钟沿输出的bit,LSB为一帧数据bit中最后一个采样沿输出bit。在器件的实际配置使用时,SPI通信需根据器件的数据手册灵活配置,对相应的数据bit根据实际要求做相应的拼接或其他处理,然后通过SPI接口输入输出。

????????在SPI通信时,主机必须根据从机的要求选择时钟极性和时钟相位,配置相同的模式。在时钟空闲状态期间(空闲状态是指传输开始时CS为高电平且在向低电平转变的期间,以及传输结束时CS为低电平且在向高电平转变的期间),对寄存器中CPOL位设置时钟信号的极性,对CPHA位设置时钟相位,根据CPHA位的状态,使用时钟上升沿或下降沿来采样和/或移位数据。如:配置主机和从机在时钟上升沿移位输出数据,在下降沿采样数据,主机MOSI在上升沿移位输出数据,将数据输出到MOSI线上,从机的MISO(和主机MOSI相连)在下降沿时采样数据(写入从机),从机MOSI(和主机MISO相连)在上升沿移位输出数据,主机MISO在下降沿采样数据(写入主机)。

二、SPI数据传输实现原理

????????SPI主从数据传输框图如图13所示。

????????(1)SSPSR 泛指 SPI 设备内部的移位寄存器(Shift Register)。它的作用是根据设置好的数据位宽(bit-width) 及SPI 时钟信号状态把数据移入或者移出 SSPBUF,每次移动的数据大小由 Bus-Width 以及 Channel-Width 所决定。

????????Bus-Width 的作用是指定地址总线到 Master(主)设备之间数据传输的单位。例如, 我们想要往 Master(主)设备里面的 SSPBUF 写入 16 Byte 大小的数据:首先,给 Master(主)设备的配置寄存器设置 Bus-Width 为 Byte;然后往 Master 设备的 Tx-Data 移位寄存器在地址总线的入口写入数据,每次写入 1 Byte 大小的数据;写完 1 Byte 数据之后,Master 设备里面的 Tx-Data 移位寄存器会自动把从地址总线传来的1 Byte 数据移入 SSPBUF 里;上述动作一共需要重复执行 16 次。

????????Channel-Width 的作用是指定 Master(主)设备与 Slave(从)设备之间数据传输的单位。与 Bus-Width 相似,Master(主)设备内部的移位寄存器会依据 Channel-Width 自动地把数据从 Master-SSPBUF 里通过 Master-SDO 管脚搬运到 Slave(从)设备里的 Slave-SDI 引脚, Slave-SSPSR 再把每次接收的数据移入 Slave-SSPBUF里。通常情况下,Bus-Width 总是会大于或等于 Channel-Width,这样能保证不会出现因 Master 与 Slave 之间数据交换的频率比地址总线与 Master 之间的数据交换频率要快,导致 SSPBUF 里面存放的数据为无效数据这样的情况。

????????(2)SSPBUF:泛指 SPI 设备里面的内部缓冲区,一般在物理上是以 FIFO 的形式,保存传输过程中的临时数据。Master(主)与 Slave(从)之间交换的数据其实都是 SPI 内部移位寄存器从 SSPBUF 里面拷贝的。可以通过往 SSPBUF 对应的寄存器 (Tx-Data / Rx-Data register) 里读写数据,间接地操控 SPI 设备内部的 SSPBUF。

????????例如,在发送数据之前,应该先往 Master(主)的 Tx-Data 寄存器写入将要发送出去的数据,这些数据会被 Master-SSPSR 移位寄存器根据 Bus-Width 自动移入 Master-SSPBUF 里,然后这些数据又会被 Master-SSPSR 根据 Channel-Width 从 Master-SSPBUF 中移出, 通过 Master-SDO 管脚传给 Slave-SDI 管脚,Slave-SSPSR 则把从 Slave-SDI 接收到的数据移入 Slave-SSPBUF 里。与此同时,Slave-SSPBUF 里面的数据根据每次接收数据的大小(Channel-Width),通过 Slave-SDO 发往 Master-SDI,Master-SSPSR 再把从 Master-SDI 接收的数据移入 Master-SSPBUF。在单次数据传输完成之后,用户程序可以通过从 Master 设备的 Rx-Data 寄存器读取 Master 设备数据交换得到的数据。

????????(3)Controller:泛指 SPI 设备里面的控制寄存器,可以通过配置它们来设置 SPI 总线的传输模式。通过时钟信号(Clock Signal)以及片选信号(Slave Select Signal)来控制 Slave(从)设备。Slave 设备会一直等待,直到接收到 Master 设备发过来的片选信号,然后根据时钟信号来工作。

????????Master(主)设备的片选操作必须由程序所实现,例如: 由程序把 SS/CS 管脚的时钟信号拉低电平,完成 SPI 设备数据通信的前期工作,当程序想让 SPI 设备结束数据通信时,再把 SS/CS 管脚上的时钟信号拉高电平。

图13 SPI主从数据传输框图

三、SPI多从机配置

????????多个从机可与单个SPI主机一起使用,从机可以采用常规模式连接或采用菊花链模式连接。

????????1、常规SPI模式:

????????在常规模式下,主机需要为每个从机提供单独的片选信号。一旦主机使能(拉低)片选信号, MOSI/MISO线上的时钟和数据便可用于所选的从机。如果使能多个片选信号,则MISO线上的数据会被破坏,因为主机无法识别哪个从机正在传输数据。从图xxx可以看出,随着从机数量的增加,来自主机的片选线的数量也增加,这会快速增加主机需要提供的输入和出数量,并限制可以使用的从机数量。该配置通常用于必须单独访问多个模数转换器 (ADC) 及数模转换器 (DAC) 的数据采集系统中。

图14 多从机SPI配置

????????2、菊花链模式:

????????在菊花链模式下,所有从机的片选信号连接在一起,因为这种配置要求所有从设备同时启用,以确保数据不间断地流经该链路中的所有移位寄存器,数据从一个从机传播到下一个从机。在此配置中,所有从机同时接收同一SPI时钟。来自主机的数据直接送到第一个从机,该从机将数据提供给下一个从机,依此类推。使用该方法时,由于数据是从一个从机传播到下一个从机,所以传输数据所需的时钟周期数与菊花链中的从机位置成比例,所需时钟周期参考器件数据手册查阅。典型应用是工业 I/O 模块中的级联多通道输入串行器与输出驱动器,但并非所有SPI器件都支持菊花链模式,使用时参阅产品数据手册以确认菊花链是否可用。

图15 多从机SPI菊花链配置

????????注:

????????TI的SPI接口是由TI公司定义的接口协议标准SSI/SSP,和SPI类似,但有部分差别,在使用时注意阅读数据手册,看接口协议是否和Motorola的SPI接口标准相同。

参考文献:

Motorola SPI Protocol:SPI-DirectC v2021.1 User Guide (microchip.com)

ADI:AN-1248,SPI Interface,AN-1248: SPI Interface | 亚德诺半导体 (analog.com)

ADI:introduction-to-spi-interface_cn.pdf(文档有错误),SPI接口简介 | 亚德诺半导体 (analog.com)

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- [蓝桥杯知识学习] 树链

- django高校宿舍管理平台(程序+开题报告)

- jmeter请求发送加密参数

- 从国际社会看ChatGPT在教育领域的未来发展方向

- Typecho后台无法登录显示503 service unavailable问题及处理

- 网络相关的计算(附例题)

- Python算法题集_盛最多水的容器

- Softing LinkXpert M3荣获Connect Professional“2023年度产品”

- 嵌入式硬件电路学习之阻抗

- 不同数据类型在内存中的存储(浮点数)