FPGA-Verilog 仿真可视化

发布时间:2023年12月27日

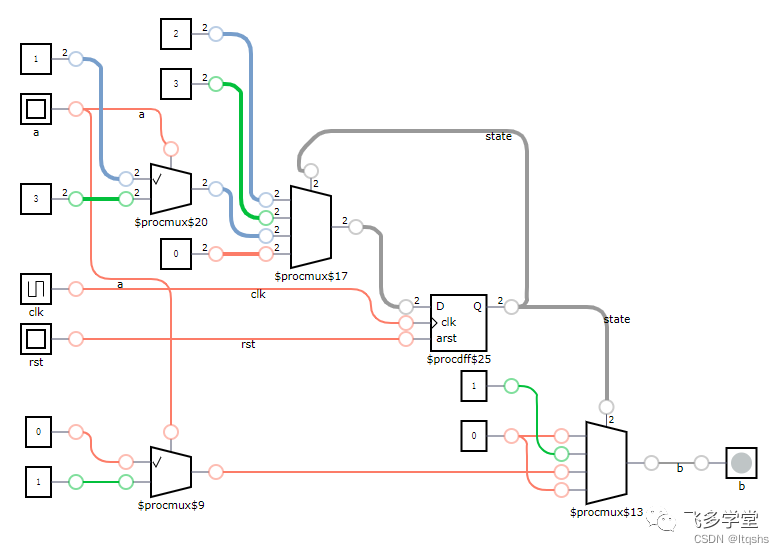

DigitalJS 是一个基于 JavaScript 实现的开源数字电路模拟器,旨在模拟由硬件设计工具(如 Yosys)合成的电路。由弗罗茨瓦夫大学的Marek Materzok开发,源文件托管于 Github 上。

DigitalJS 的开源网址如下:https://github.com/tilk/digitaljs

下面这个网址:http://digitaljs.tilk.eu/, 提供了一个 DigitalJS 的在线演示程序,可以对 Verilog/SystemVerilog 等语言进行在线综合、可视化。

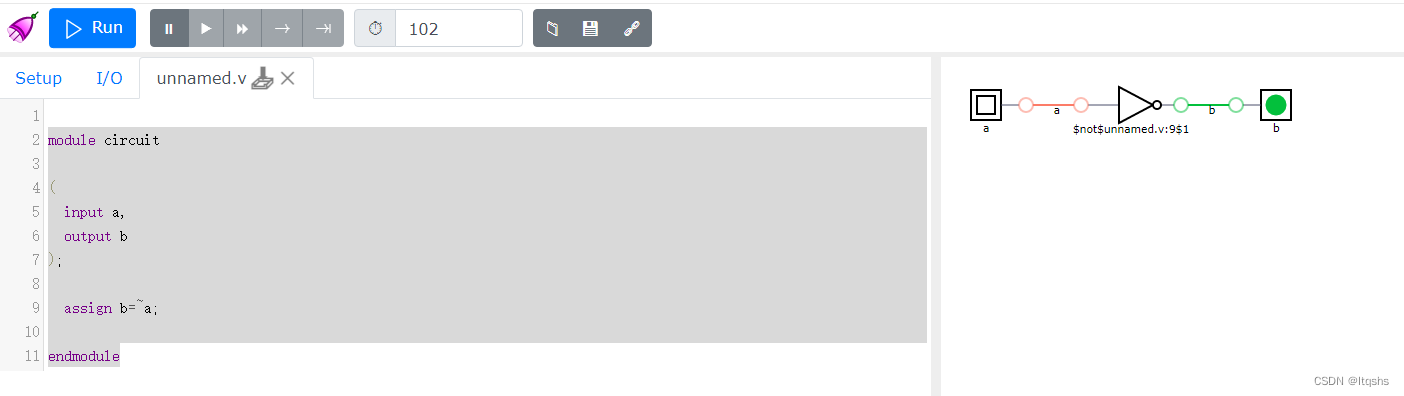

输入下面这段 Verilog 代码:

module circuit

(

input a,

output b

);

assign b=~a;

endmodule

输入上面的代码可以生成如下电路:

上图电路中,点击 a 按钮, LED b 会变为红色。

Yosys 有很多我们通常不使用的功能,包括生成带有设计原理图的 graphviz 文件的能力,尽管它们并不像这样清晰。很高兴看到它与Falstad 作为模拟引擎结合在一起。

yosys2digitaljs: 该程序将由Yosys电路综合软件生成的JSON网表输出转换为DigitalJS图形电路模拟器可用。

还有一个在线 Verilog 编辑仿真软件:EDA Playground, 网址是:https://www.edaplayground.com/, 需要登录才能进入。

参考原文:《Verilog 仿真可视化》

文章来源:https://blog.csdn.net/qq_21794157/article/details/135234076

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!