国科大计算机体系结构期末考试——更新中

发布时间:2024年01月08日

题型一、第二章的画图

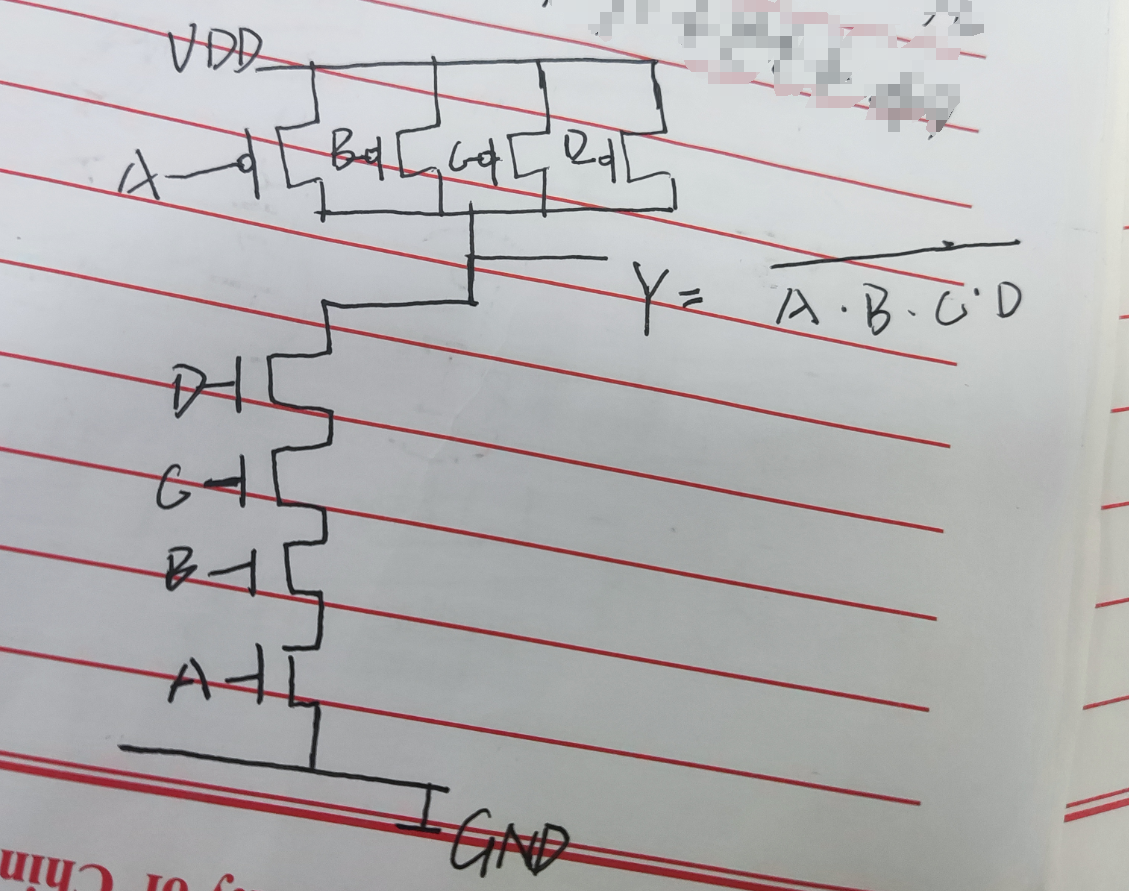

给一个逻辑表达式,画出晶体管级别的电路图

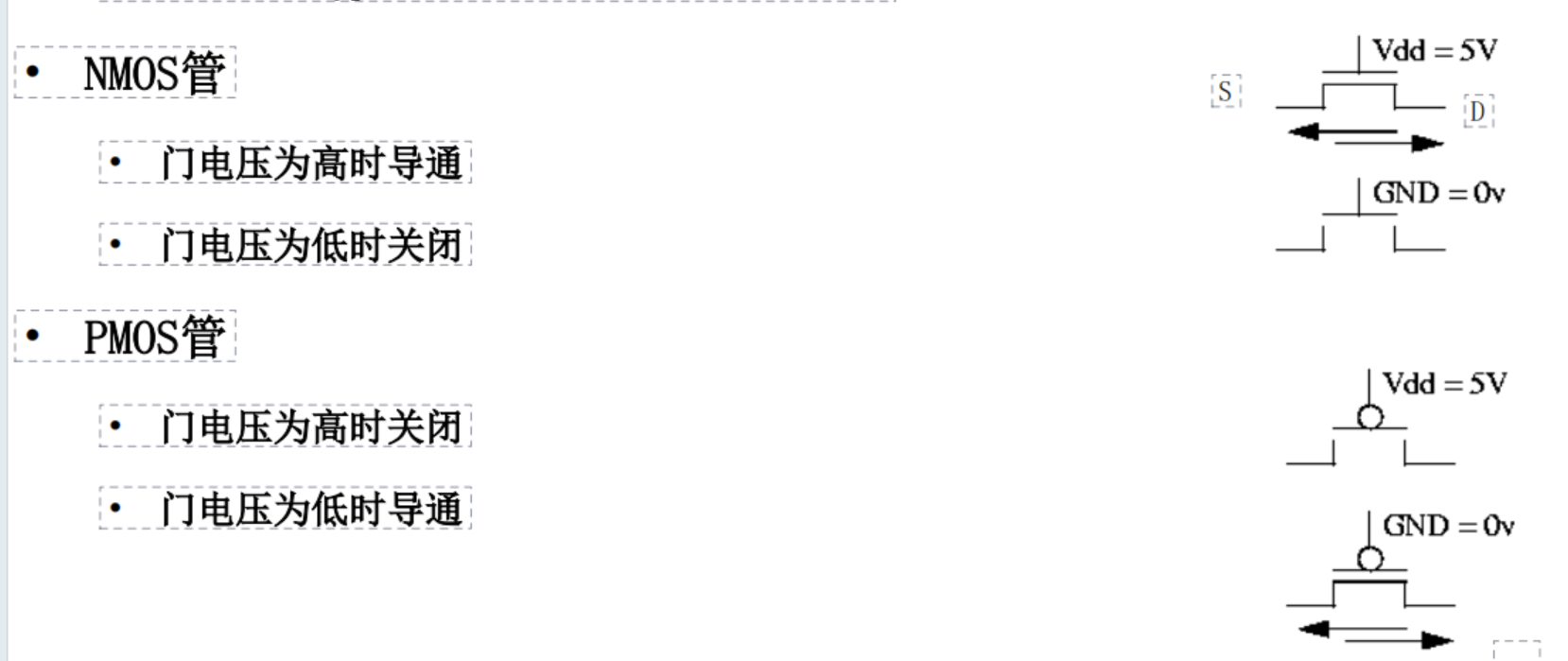

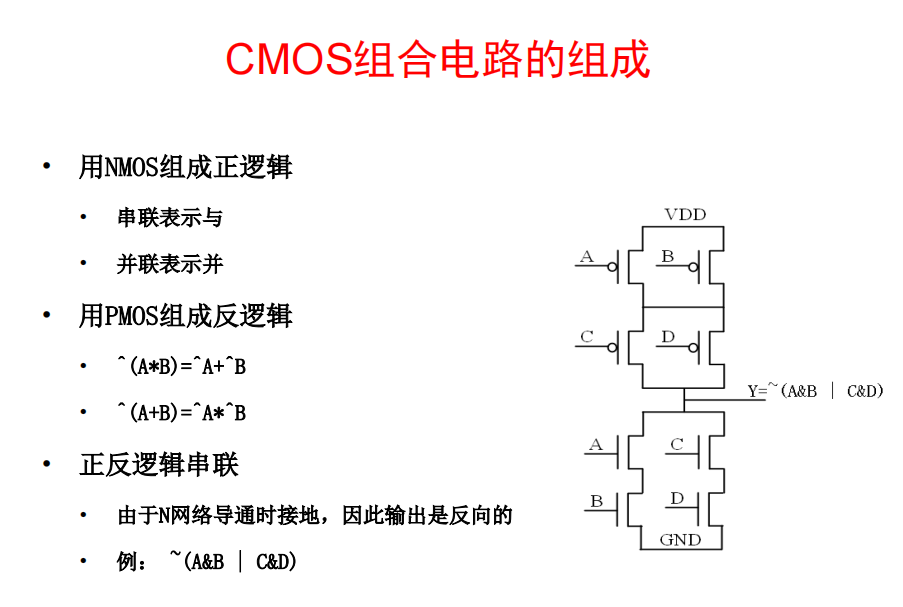

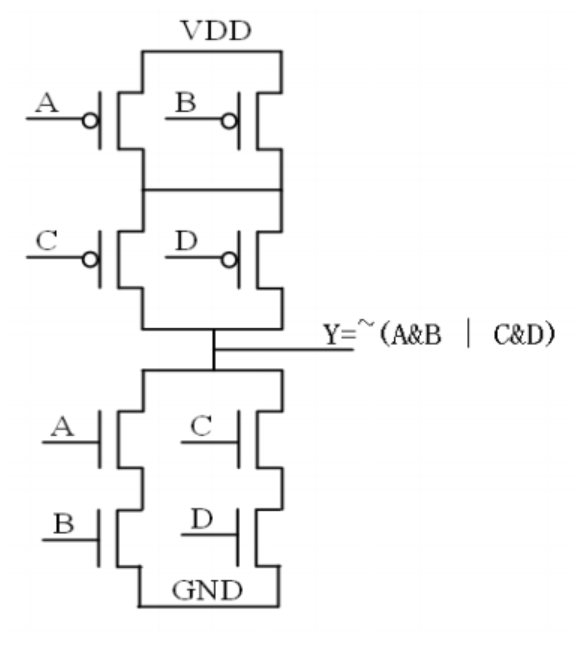

cmos电路的基本电路:

与非门的功能是对多个输入信号进行逻辑与操作,然后对结果进行取反。

或非门的功能是对多个输入信号进行逻辑或操作,然后对结果进行取反。

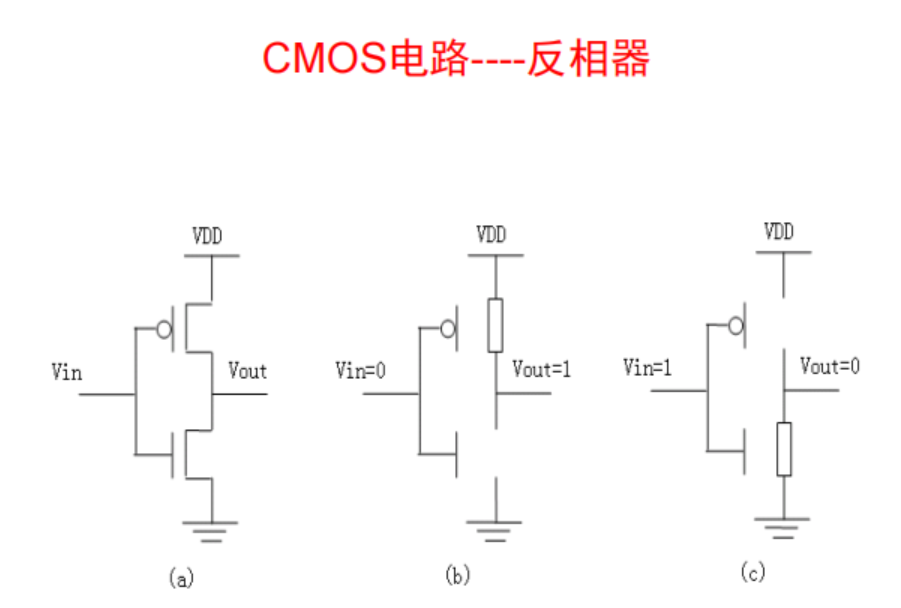

非门(NOT gate),也称为反相器(inverter)

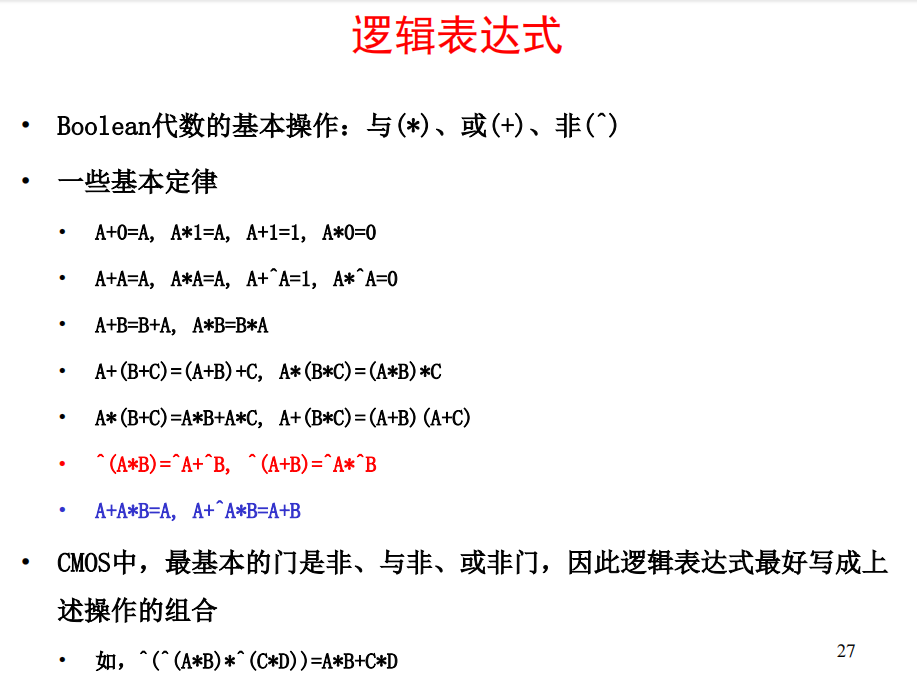

将表达式用CMOS支持的门表示

所以与门有两级延迟,因为

与门需要用与非门和非门串联实现

或门需要用或非门和非门串联实现

上图中重要的这一条,AB的与的非等于AB分别取非然后或,相当于非 把括号里面的东西都非了一遍

AB的或的非,等于AB分别非的与

怎么画

难道这样表示

如果是反向n管变成p管,串联变成并联,接地GND变成接入VDD,

都是N管接地,P管接电

正反逻辑串联等于整个表达式的非

如上图,下面一半是N管的表达,上面一半是P管的表达,正反逻辑串联起来,得到表达式的非?

两级与非表达与或

例子

这个用了8个晶体管,因为

是这个与非门的电路图

题型二、 第二章触发器相关计算(较难,可能不考)

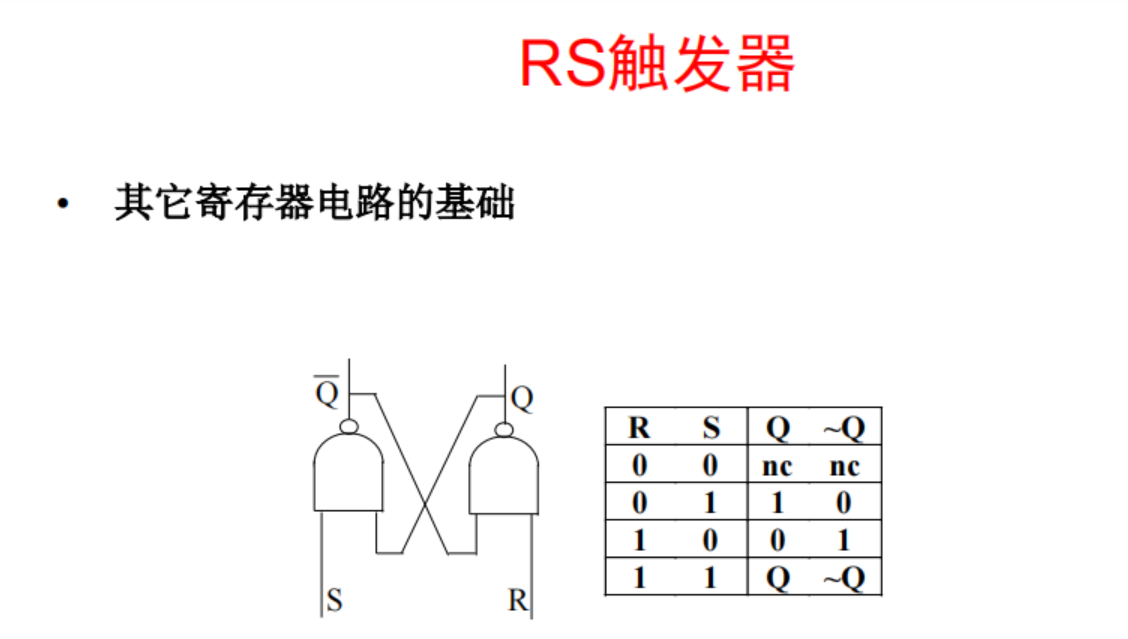

RS触发器

nc表示not care 不关心状态

R表示reset,S表示Setup

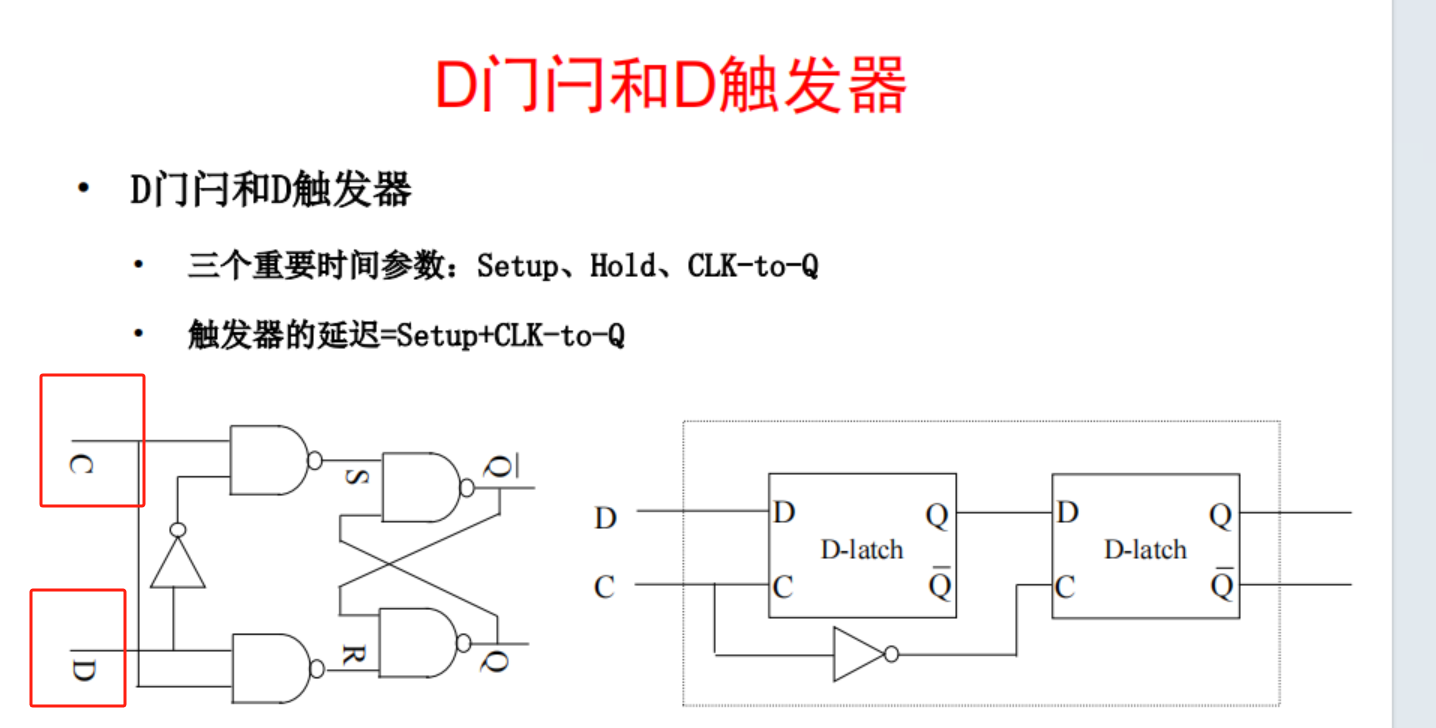

RS触发器组合形成D触发器

C为时钟,D是数据,个人感觉C的意思更像是Control,控制

意思是,在C等于1的时候,D能把值传递给Q,如果C=0,S和R一直等于1,原来的值不变

这是一个非门,不是二极管!!

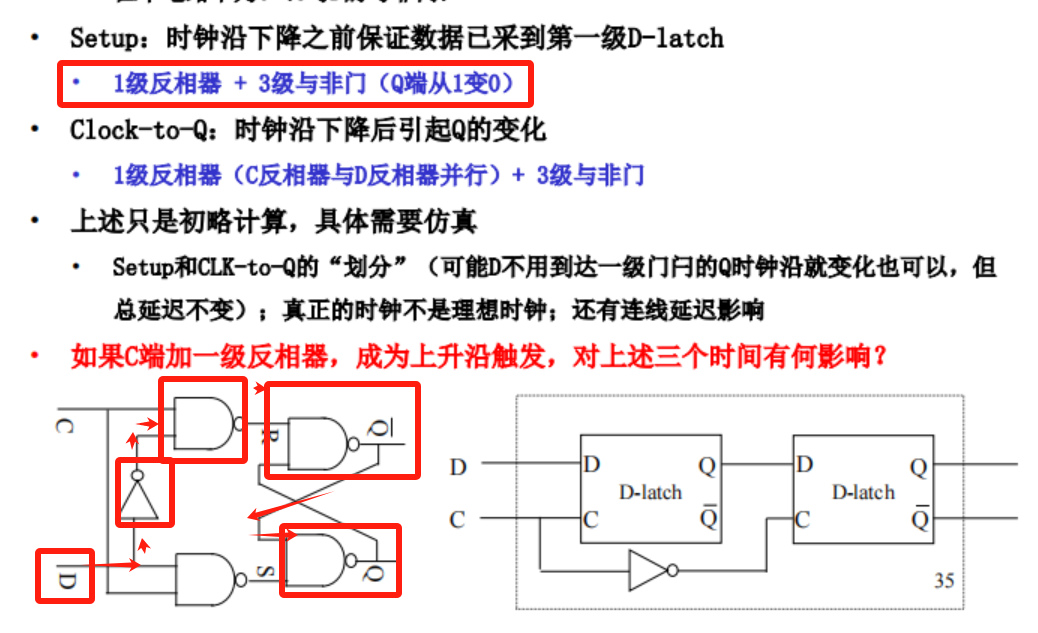

相关参数理解和计算

之前写verilog在FPGA上仿真就碰到过这个情况,上升沿来了,但是值没有存好,今天正好看看

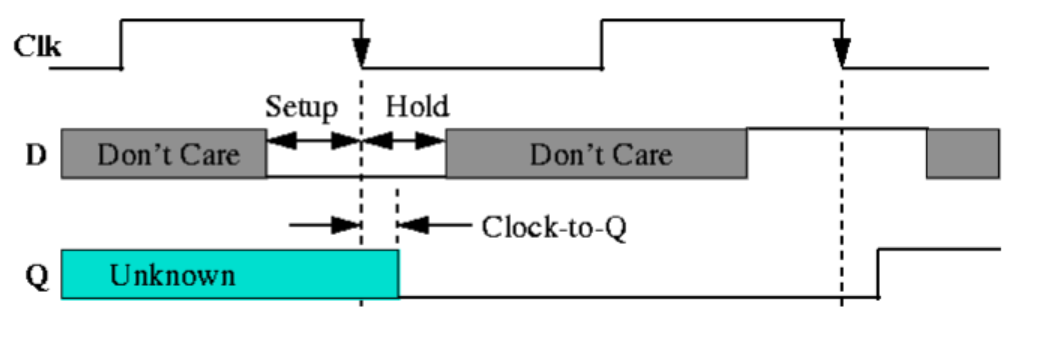

setup time: 在C变化由1变零之前,D要把数据存到第一个D里面,因为后面C变成0之后,就不能再存数据了。D的值在被采集采集完毕之前,需要setup坚挺的时间,我的理解是需要的采集到第一个Q的需要的时间。

hold time:被采集后需要保持的时间,我认为是从第一个Q到第二个Q的时间

clock to q:是在下图

触发器的延迟等于setuptime + clock to q,但是也要保持住hold time

文章来源:https://blog.csdn.net/weixin_44357071/article/details/135431159

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 复试 || 就业day03(2023.12.29)算法篇

- freeRTOS使用互斥锁(Mutex)解决多任务竞争冒险

- 2023年第十六届山东省职业院校技能大赛高职组“应用软件系统开发”赛项样题

- arcgis 线要素shp数据处理

- 几行Python代码,轻松搞定Excel表格数据去重

- 自适应批量生成二维码源码系统:电脑+手机端自适应 支持任何类型批量生成二维码 附带完整的搭建教程

- Notepad++ v7.7.1 安装及添加插件

- ReTree:扩散模型 + 视网膜图像生成

- crmeb v5新增一个功能的完整示例记录

- 【深度学习目标检测】五、基于深度学习的安全帽识别(python,目标检测)