「Verilog学习笔记」加减计数器

发布时间:2023年12月17日

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

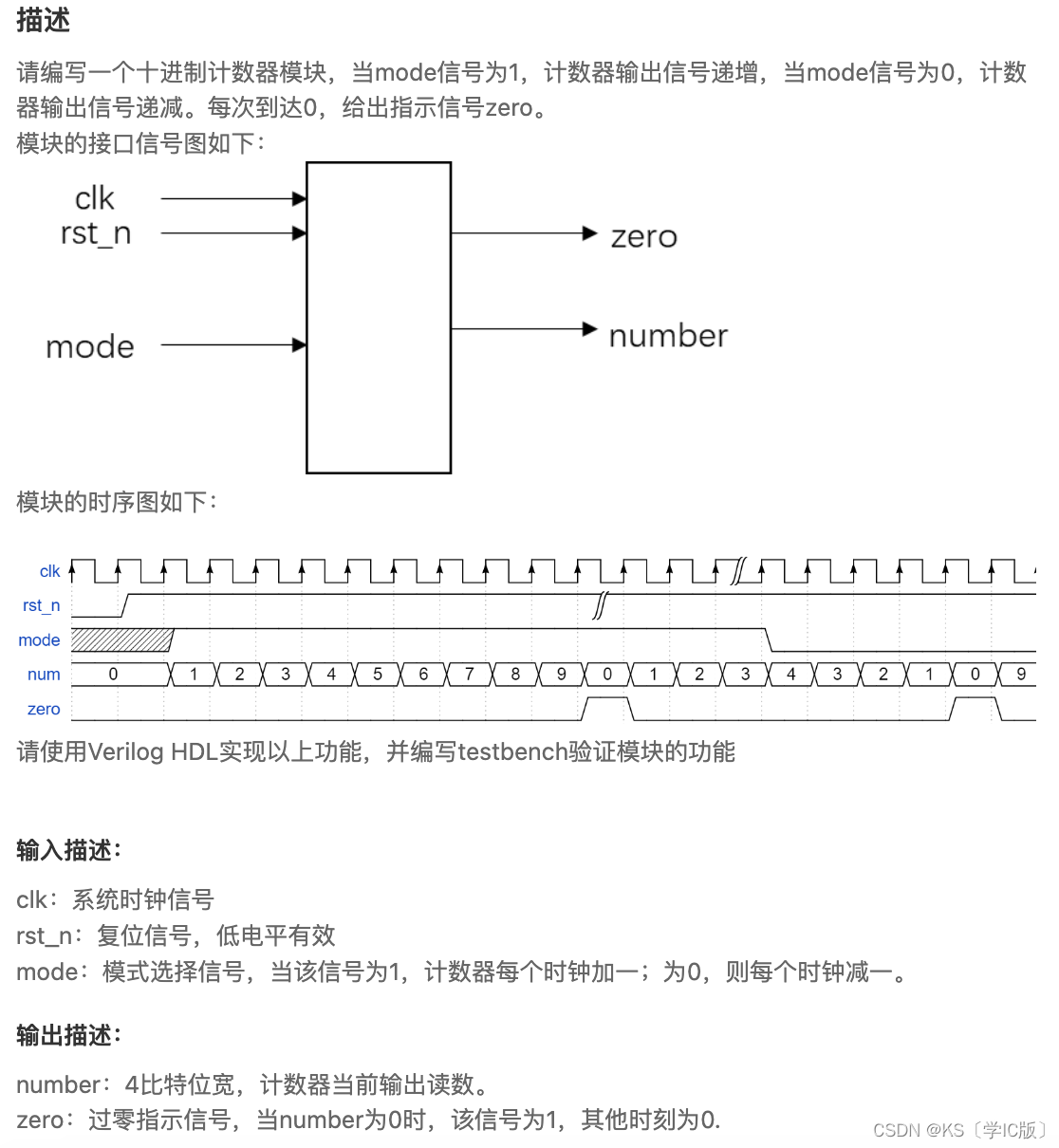

`timescale 1ns/1ns

module count_module(

input clk,

input rst_n,

input mode,

output reg [3:0]number,

output reg zero

);

reg [3:0] num ;

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) num <= 0 ;

else

if (mode) num <= num == 9 ? 0 : num + 1 ;

else num <= num == 0 ? 9 : num - 1 ;

end

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) number <= 0 ;

else number <= num ; // 题目有误 根据答案波形图 将输出打一拍后输出

end

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) zero <= 0 ;

else zero <= num == 0 ; // 同理 当num == 0时 下一拍number才会等于0 根据非阻塞赋值的特性 将会在下一拍输出zero = 1

end

endmodule

文章来源:https://blog.csdn.net/m0_54689021/article/details/135003230

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:chenni525@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- Hive之set参数大全-9

- Android笔记(二十三):Paging3分页加载库结合Compose的实现分层数据源访问

- spring gateway整合knife4j-gateway访问/doc.html报错404问题

- Node.js下载安装教程

- Towards Robust Blind Face Restoration with Codebook Lookup Transformer

- 【STC8A8K64D4开发板】第2-9讲:比较器

- 互联网架构演变过程

- polar CTF CB链

- 蓝牙物联网通信网络设计方案

- day08 反转字符串 反转字符串Ⅱ 替换数字 翻转字符串里的单词 右旋转字符串